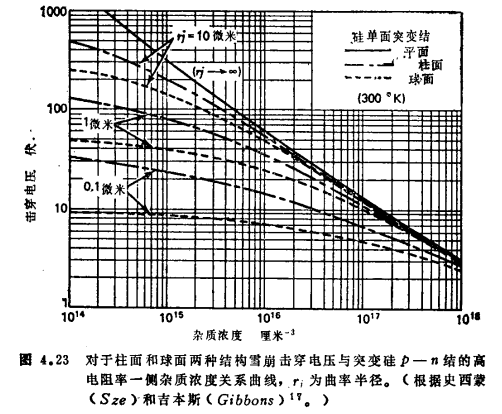

MOS管P-N结曲率击穿电压,由于几何因素的影响,扩散平面p-n结的典型雪崩击穿电压远低于图4.20对一维硅阶跃结给出的数据。用常规平面工艺技术形成p-n结的方法是:使高浓度的杂质原子通过二氧化硅掩膜层上的矩形“窗口”向极性相反的硅衬底扩散。采用这种工艺技术时,会从“窗口”边缘进行横向扩散,其扩散距离近似等于在硅衬底本体内进行垂直扩散的距离。因此,在这样的平面结构中,横向扩散量可与结深相比较,而且

MOS管P-N结曲率击穿电压,由于几何因素的影响,扩散平面p-n结的典型雪崩击穿电压远低于图4.20对一维硅阶跃结给出的数据。用常规平面工艺技术形成p-n结的方法是:使高浓度的杂质原子通过二氧化硅掩膜层上的矩形“窗口”向极性相反的硅衬底扩散。采用这种工艺技术时,会从“窗口”边缘进行横向扩散,其扩散距离近似等于在硅衬底本体内进行垂直扩散的距离。因此,在这样的平面结构中,横向扩散量可与结深相比较,而且

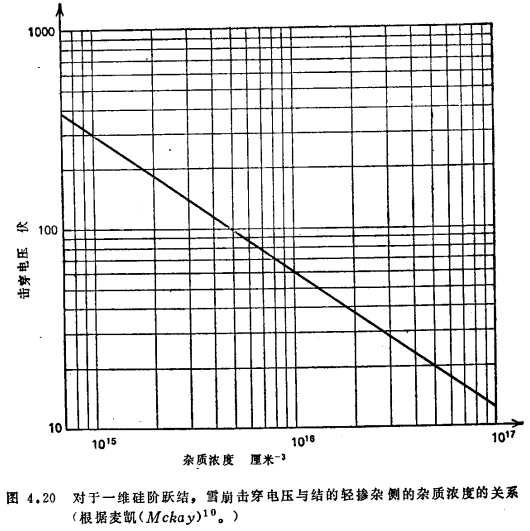

详解MOS管一维突变p-n结的雪崩击穿电压及主要原因,对于在饱和漏电流区工作的MOS器件,如果不断地增加漏极外加电压,则漏极电压最终将增高到足以产生漏二极管的雪崩击穿,且能看到漏电流迅速增加。众所周知,在反偏压p-n结上发生雪崩击穿时的电压在很大程度上依赖于结的高电阻率一侧的掺杂浓度,特别是将随掺杂浓度的增加而下降。MOS管PN结雪崩击穿。这点不难从图4.20看出,其中总结了由麦凯(Mckay)1

详解MOS管一维突变p-n结的雪崩击穿电压及主要原因,对于在饱和漏电流区工作的MOS器件,如果不断地增加漏极外加电压,则漏极电压最终将增高到足以产生漏二极管的雪崩击穿,且能看到漏电流迅速增加。众所周知,在反偏压p-n结上发生雪崩击穿时的电压在很大程度上依赖于结的高电阻率一侧的掺杂浓度,特别是将随掺杂浓度的增加而下降。MOS管PN结雪崩击穿。这点不难从图4.20看出,其中总结了由麦凯(Mckay)1

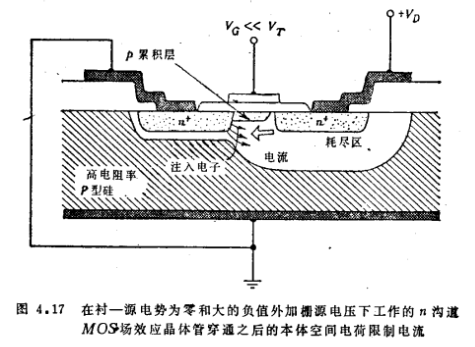

MOS管漏极耗尽区漏极耗尽区发生穿通效应后,由漏区到源区的空间电荷限制电流如果MOS场效应晶体管的漏源间距足够小,用以制作器件的衬底的电阻率足够高,与反偏压漏一衬结有关的耗尽区会随漏压增加而扩展,以致最后将同源一衬结的耗尽区联通。这个条件通常称为穿通,见图4.11所示硅n沟道MOS场效应晶体管截面图。在超出穿通需要不断增加正值的外加漏电压时,源区内的多数载流子,这种情形为电子,可以注入到耗尽沟道区

MOS管漏极耗尽区漏极耗尽区发生穿通效应后,由漏区到源区的空间电荷限制电流如果MOS场效应晶体管的漏源间距足够小,用以制作器件的衬底的电阻率足够高,与反偏压漏一衬结有关的耗尽区会随漏压增加而扩展,以致最后将同源一衬结的耗尽区联通。这个条件通常称为穿通,见图4.11所示硅n沟道MOS场效应晶体管截面图。在超出穿通需要不断增加正值的外加漏电压时,源区内的多数载流子,这种情形为电子,可以注入到耗尽沟道区

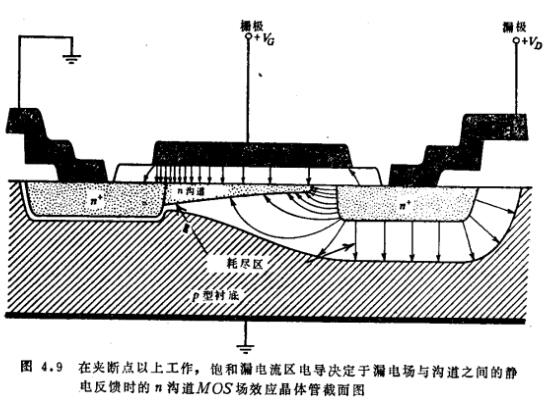

MOS场效应晶体管漏区电场对沟道区的静电反馈,已经证明,对于采用低电阻率衬底制成的MOS场效应晶体管,促使其漏极饱和电阻随漏-源间距的减小而缩小的主要机理是沟道漏端附近耗尽区扩展对导电沟道有效长度的调制作用3。然而对于用中等高电阻率衬底制成的器件,起决定作用的则是另外一种机理。这一机理加上沟道长度受到调制的效应可以使漏极饱和电阻进一步下降3,4。为此缘故,制作于轻掺杂衬底而且沟道长度很短的MOS场

MOS场效应晶体管漏区电场对沟道区的静电反馈,已经证明,对于采用低电阻率衬底制成的MOS场效应晶体管,促使其漏极饱和电阻随漏-源间距的减小而缩小的主要机理是沟道漏端附近耗尽区扩展对导电沟道有效长度的调制作用3。然而对于用中等高电阻率衬底制成的器件,起决定作用的则是另外一种机理。这一机理加上沟道长度受到调制的效应可以使漏极饱和电阻进一步下降3,4。为此缘故,制作于轻掺杂衬底而且沟道长度很短的MOS场

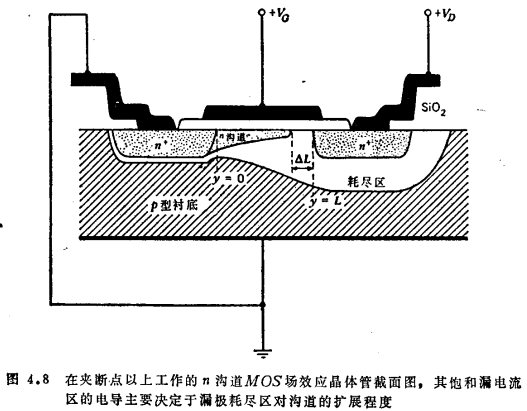

MOS管沟道长度调制效应,在外加漏极电压超过夹断电压之后,在沟道末端漏极扩散区附近形成-耗尽区,而且随VD的增加该耗尽区向源极扩散区扩展。只要漏-源间距远大于漏耗尽区宽度,沟道导电部分长度总的减少是十分微小的,而且在一级近似范围内,饱和漏电流等于常数,且与漏电压无关。然而,当漏-源间距减小到可与给定漏电压下漏极耗尽区宽度相比拟时,有效沟道长度随VD增加而引起的减小就不能忽略了。随着沟道导电部分有效

MOS管沟道长度调制效应,在外加漏极电压超过夹断电压之后,在沟道末端漏极扩散区附近形成-耗尽区,而且随VD的增加该耗尽区向源极扩散区扩展。只要漏-源间距远大于漏耗尽区宽度,沟道导电部分长度总的减少是十分微小的,而且在一级近似范围内,饱和漏电流等于常数,且与漏电压无关。然而,当漏-源间距减小到可与给定漏电压下漏极耗尽区宽度相比拟时,有效沟道长度随VD增加而引起的减小就不能忽略了。随着沟道导电部分有效

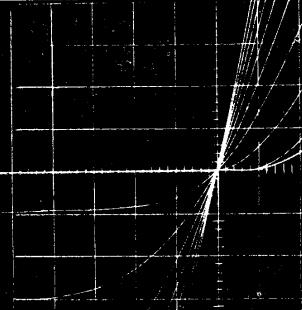

MOS场效应晶体管夹断点以上随外加漏-源电压而变的电导不完全饱和电流:在夹断点以上随外加漏-源电压而变的电导一般说来,当外加漏电压大于夹断电压时,只有在沟道非常长的MOS场效应晶体管中才能观察到漏电流完全饱和的现象。然而当MOS场效应晶体的漏-源间距L逐步减小,夹断以上的漏电流饱和特性将迅速发生畸变。对于用高电阻率衬底制作的MOS器件来说尤其是这样,在夹断点以上工作的MOS场效应晶体管,使其饱和电

MOS场效应晶体管夹断点以上随外加漏-源电压而变的电导不完全饱和电流:在夹断点以上随外加漏-源电压而变的电导一般说来,当外加漏电压大于夹断电压时,只有在沟道非常长的MOS场效应晶体管中才能观察到漏电流完全饱和的现象。然而当MOS场效应晶体的漏-源间距L逐步减小,夹断以上的漏电流饱和特性将迅速发生畸变。对于用高电阻率衬底制作的MOS器件来说尤其是这样,在夹断点以上工作的MOS场效应晶体管,使其饱和电

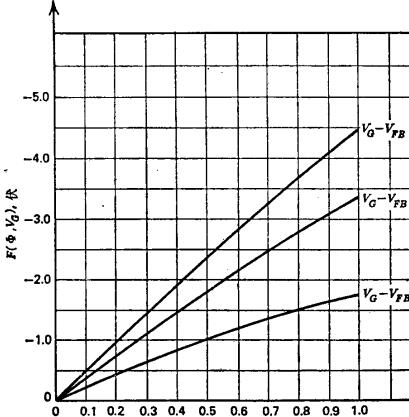

MOS场效应晶体管作为栅压函数的饱和漏电流的关系将(4.26)代入(4.14)可以将饱和漏-源电流表示成外加栅-源电压函数的形式。结果是而可以表示成式中函数F(ф,VG)定义为栅压减平带电压取三个不同的数值时,F(ф,VG)与ф之间的函数关系表示在图4.6中。(考察(4.27),显然F(ф,VG)总是小于或等于零。)结合(4.36)和(4.37)得到或对于用中等高电阻率p型衬底制作的n沟道MOS场

MOS场效应晶体管作为栅压函数的饱和漏电流的关系将(4.26)代入(4.14)可以将饱和漏-源电流表示成外加栅-源电压函数的形式。结果是而可以表示成式中函数F(ф,VG)定义为栅压减平带电压取三个不同的数值时,F(ф,VG)与ф之间的函数关系表示在图4.6中。(考察(4.27),显然F(ф,VG)总是小于或等于零。)结合(4.36)和(4.37)得到或对于用中等高电阻率p型衬底制作的n沟道MOS场

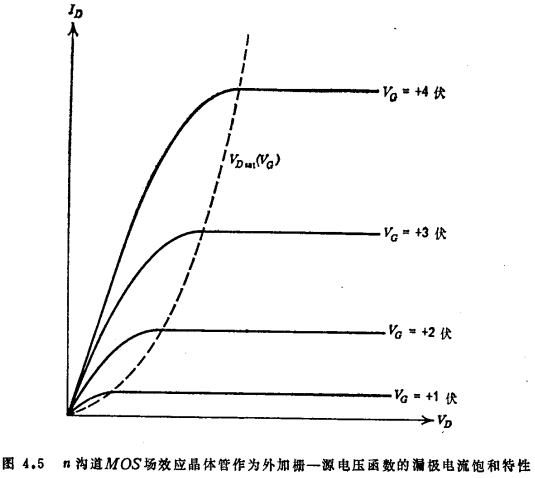

饱和漏电流区的电导在前一节中,已经证明当栅-源电势保持常数,而漏极电压从零开始增加时,漏-源微分电导逐渐减小,直到电流达到饱和。在一级近似范围内,如果漏电压大于,而小于漏极二极管击穿电压(漏衬组成的二极管承受的反向偏压),则漏-源电流与外加漏极电压无关。参考图4.4,即不难理解漏-源电流饱和的物理基础。如图4.4(a)所示,对于用的中等高电阻率衬底制作的n沟道MOS场效应晶体管,在外加正值栅压(+

饱和漏电流区的电导在前一节中,已经证明当栅-源电势保持常数,而漏极电压从零开始增加时,漏-源微分电导逐渐减小,直到电流达到饱和。在一级近似范围内,如果漏电压大于,而小于漏极二极管击穿电压(漏衬组成的二极管承受的反向偏压),则漏-源电流与外加漏极电压无关。参考图4.4,即不难理解漏-源电流饱和的物理基础。如图4.4(a)所示,对于用的中等高电阻率衬底制作的n沟道MOS场效应晶体管,在外加正值栅压(+

MOS场效应晶体管略低于饱和情况的漏-源电导的特性详解在外加栅极电压保持常数,漏源电压增加时,微分电导逐渐变小,测得的漏极电流开始饱和。因此,(4.20)和(4.21)不再成立,可变电阻的线性关系开始发生畸变。在此情况下,对在漏源电压极低条件下得出的近似表达式不再成立,作为一个整体必须用(4.14)式来计算漏极电流。方程(4.14)可以写成式中参数k和Δ的定义是和Δ可以看成MOS场效应晶体管以栅压

MOS场效应晶体管略低于饱和情况的漏-源电导的特性详解在外加栅极电压保持常数,漏源电压增加时,微分电导逐渐变小,测得的漏极电流开始饱和。因此,(4.20)和(4.21)不再成立,可变电阻的线性关系开始发生畸变。在此情况下,对在漏源电压极低条件下得出的近似表达式不再成立,作为一个整体必须用(4.14)式来计算漏极电流。方程(4.14)可以写成式中参数k和Δ的定义是和Δ可以看成MOS场效应晶体管以栅压

MOS场效应晶体管漏极电压低时的漏-源电导的工作状态方程(4.14)是描述n沟道MOS场效应晶体管,在低于饱和电流漏电压的所有漏压值下工作的情况。应用类似的方法,可以得到在低于饱和电流下工作的p沟道场效应晶体管漏极电流的表达式。对于很低的漏源电压值和由此得到因此,外加漏源电势非常小时,电流-电压关系近似等于注意到下式是有意义的也就是说,在强反型条件下,单位面积耗尽区电荷等于-Cox(2фF)1/2

MOS场效应晶体管漏极电压低时的漏-源电导的工作状态方程(4.14)是描述n沟道MOS场效应晶体管,在低于饱和电流漏电压的所有漏压值下工作的情况。应用类似的方法,可以得到在低于饱和电流下工作的p沟道场效应晶体管漏极电流的表达式。对于很低的漏源电压值和由此得到因此,外加漏源电势非常小时,电流-电压关系近似等于注意到下式是有意义的也就是说,在强反型条件下,单位面积耗尽区电荷等于-Cox(2фF)1/2