MOS管漏-源电外加漏极电压低于饱和条件时MOS晶体管的工作状况图4.1表示在较低的外加漏-源电压下工作时n-沟道MOS场效晶体管的截面图。因为栅-漏之间电势差稍小于栅-源之间电势差,栅极绝缘物内沿x方向的电场强度随着y从沟道源端y=0增加到沟道漏端y=L而相应地减少,从而如图所示,沟道源端附近的微分电导将大于沟道漏端附近的微分电导。长度为dy宽度为W的沟道元的微分电阻等于式中Qn(y)是作为y的

MOS管漏-源电外加漏极电压低于饱和条件时MOS晶体管的工作状况图4.1表示在较低的外加漏-源电压下工作时n-沟道MOS场效晶体管的截面图。因为栅-漏之间电势差稍小于栅-源之间电势差,栅极绝缘物内沿x方向的电场强度随着y从沟道源端y=0增加到沟道漏端y=L而相应地减少,从而如图所示,沟道源端附近的微分电导将大于沟道漏端附近的微分电导。长度为dy宽度为W的沟道元的微分电阻等于式中Qn(y)是作为y的

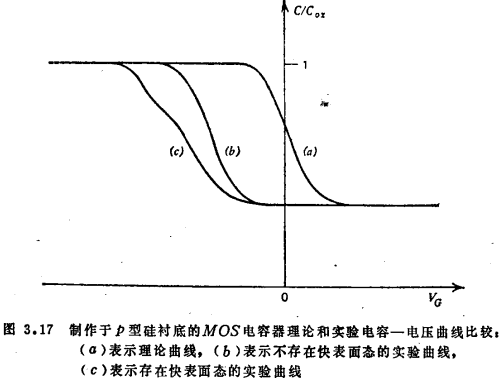

MOS电容器结构的电容-电压关系特性的研究已经成为探索半导体表面的一种非常有力的工具。使用这种技术通常只需要制备一个比较简单的MOS电容器结构,但是所得到的全部结果实际上都可以直接应用到更为复杂的MOS场效应晶体管。这项技术是基于如下的事实:即只要把由半导体衬底制作的MOS电容器的理论电容-电压关系和实际的实验观测C-V曲线比较一下,就能确定半导体-绝缘物界面的重要电学性质。

MOS电容器结构的电容-电压关系特性的研究已经成为探索半导体表面的一种非常有力的工具。使用这种技术通常只需要制备一个比较简单的MOS电容器结构,但是所得到的全部结果实际上都可以直接应用到更为复杂的MOS场效应晶体管。这项技术是基于如下的事实:即只要把由半导体衬底制作的MOS电容器的理论电容-电压关系和实际的实验观测C-V曲线比较一下,就能确定半导体-绝缘物界面的重要电学性质。

MOS电容器深耗尽条件下的栅-衬电容如栅极绝缘物有些“漏电”,甚至有一微弱的稳态电流由栅极流到衬底,或者,如栅压从对应于累积的偏压范围非常迅速地转换为在稳态条件下正常地产生反型的数值,则MOS电容器结构是工作在深耗尽状态。如果在前一情况,少数载流子无法在硅表面累积,或者在后一种(暂态)情况,如果在少数载流子还未来得及在硅表面累积之前就测量电容,则栅极电场必须用表面耗尽区电荷来终止。在这样条件下,

MOS电容器深耗尽条件下的栅-衬电容如栅极绝缘物有些“漏电”,甚至有一微弱的稳态电流由栅极流到衬底,或者,如栅压从对应于累积的偏压范围非常迅速地转换为在稳态条件下正常地产生反型的数值,则MOS电容器结构是工作在深耗尽状态。如果在前一情况,少数载流子无法在硅表面累积,或者在后一种(暂态)情况,如果在少数载流子还未来得及在硅表面累积之前就测量电容,则栅极电场必须用表面耗尽区电荷来终止。在这样条件下,

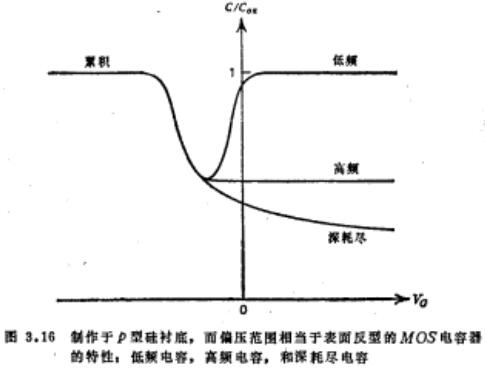

MOS电容器在高频时的栅-衬电容及其电压关系分析对于这样的频率,表面反型层电荷不随栅极信号而变化。MOS电容器高频。因此,对于高频栅极信号,3.2.4节的结果(这些结果是基于系统处于热平衡状态的假设)不再有效。因为反型层电荷密度不随栅极电压的高频变化,对于一个给定的直流偏压,可以假定为一常数。换言之,在反型条件下交流电场须由表面耗尽区的电荷来终止。在这些条件下,耗尽区单位面积电荷密度和耗尽区宽度将

MOS电容器在高频时的栅-衬电容及其电压关系分析对于这样的频率,表面反型层电荷不随栅极信号而变化。MOS电容器高频。因此,对于高频栅极信号,3.2.4节的结果(这些结果是基于系统处于热平衡状态的假设)不再有效。因为反型层电荷密度不随栅极电压的高频变化,对于一个给定的直流偏压,可以假定为一常数。换言之,在反型条件下交流电场须由表面耗尽区的电荷来终止。在这些条件下,耗尽区单位面积电荷密度和耗尽区宽度将

MOS电容器在低频时的栅-衬电容及其电压关系分析对于这样的频率,反型层电荷随栅极信号的变化,热平衡条件成立。记得制作于p型衬底的MOS器件单位面积总的表面空间电荷密度是由(2.19)式给出,由此可知通过(2.19)和(3.11)式可以得到与表面空间电荷区有关的单位面积电容。MOS电容器低频。简单的微分可以得到式中和是х=0时半导体表面载流子浓度,而方程(3.18)可以用表成MOS电容器的低频(平衡

MOS电容器在低频时的栅-衬电容及其电压关系分析对于这样的频率,反型层电荷随栅极信号的变化,热平衡条件成立。记得制作于p型衬底的MOS器件单位面积总的表面空间电荷密度是由(2.19)式给出,由此可知通过(2.19)和(3.11)式可以得到与表面空间电荷区有关的单位面积电容。MOS电容器低频。简单的微分可以得到式中和是х=0时半导体表面载流子浓度,而方程(3.18)可以用表成MOS电容器的低频(平衡

详解MOS管结构电容频率函数的栅-衬电容的变化特性在累积或耗尽条件下,用以终止半导体表面栅极电场的电荷是来自衬底的多数载流子。因此,在半导体表面将跟随栅极上的外加高频交流信号而感生电荷,只要式中τD为与半导体衬底有关的介电驰豫时间。(材料的介电驰豫时间τD等于介电常数乘以其电阻率。例如,电阻率为5-欧姆-厘米的硅,τD等于5×10-12秒。)在反型条件下,情况完全不同,现在,终止栅极电场的电荷是由

详解MOS管结构电容频率函数的栅-衬电容的变化特性在累积或耗尽条件下,用以终止半导体表面栅极电场的电荷是来自衬底的多数载流子。因此,在半导体表面将跟随栅极上的外加高频交流信号而感生电荷,只要式中τD为与半导体衬底有关的介电驰豫时间。(材料的介电驰豫时间τD等于介电常数乘以其电阻率。例如,电阻率为5-欧姆-厘米的硅,τD等于5×10-12秒。)在反型条件下,情况完全不同,现在,终止栅极电场的电荷是由

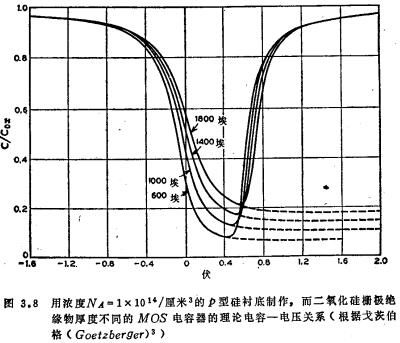

MOS电容器栅-衬电容对栅极电压的依赖关系外加栅极电压与表面势фS,绝缘物中的电压降VOS,金属-半导体功函数差фMS’之间的关系为再有,因为外加栅-衬电压所引起的电场全部位于栅极,栅极绝缘物和半导体表面所组成的区域内,在这个区域内电荷中性条件是:式中等于栅电极单位面积电荷密度与VOS关系是结合(2.42),(3.4)和(2.43)得到方程(3.5)可用平带电压来表示单位面积栅一衬电容可以写成可从

MOS电容器栅-衬电容对栅极电压的依赖关系外加栅极电压与表面势фS,绝缘物中的电压降VOS,金属-半导体功函数差фMS’之间的关系为再有,因为外加栅-衬电压所引起的电场全部位于栅极,栅极绝缘物和半导体表面所组成的区域内,在这个区域内电荷中性条件是:式中等于栅电极单位面积电荷密度与VOS关系是结合(2.42),(3.4)和(2.43)得到方程(3.5)可用平带电压来表示单位面积栅一衬电容可以写成可从

解析半导体功函数差对MOS电容器特性的影响,在氧化——硅界面上的固定正电荷密度和栅电极——硅衬底之间的功函数差,这两个因素对于MOS器件的表面空间电荷区都有明显的影响。如上所述,对于一个相当大的数值区域内的衬底电阻率和各种不同的晶体取向的n型或p型硅片,已经从实验观测到单位面积正值界面电荷Qss的存在(Qss的实际物理性质将在后面的一章讨论),因为这个电荷密度恒为正值,总能在硅表面感生一个电量相等

解析半导体功函数差对MOS电容器特性的影响,在氧化——硅界面上的固定正电荷密度和栅电极——硅衬底之间的功函数差,这两个因素对于MOS器件的表面空间电荷区都有明显的影响。如上所述,对于一个相当大的数值区域内的衬底电阻率和各种不同的晶体取向的n型或p型硅片,已经从实验观测到单位面积正值界面电荷Qss的存在(Qss的实际物理性质将在后面的一章讨论),因为这个电荷密度恒为正值,总能在硅表面感生一个电量相等

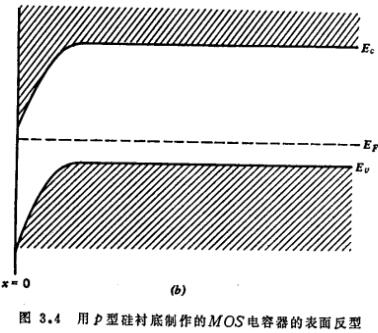

将MOS电容器电容值作成电压函数关系曲线时,存在三个有趣的区域。这里讨论用p型衬底制作的MOS电容器的情形,而用n型衬底制作的类似器件也可用同样的方法处理。MOS电容器累积,对于足够大的负栅极电压,作为多数载流子的空穴被吸引到硅表面,终止于栅极绝缘物上的电场;结果在硅表面形成如图3.2(a)所示的p型累积层。因为外加栅极电压引起空穴浓度的增加,硅表面附近的费密能级将移向更加接近价带边缘的位置。由于

将MOS电容器电容值作成电压函数关系曲线时,存在三个有趣的区域。这里讨论用p型衬底制作的MOS电容器的情形,而用n型衬底制作的类似器件也可用同样的方法处理。MOS电容器累积,对于足够大的负栅极电压,作为多数载流子的空穴被吸引到硅表面,终止于栅极绝缘物上的电场;结果在硅表面形成如图3.2(a)所示的p型累积层。因为外加栅极电压引起空穴浓度的增加,硅表面附近的费密能级将移向更加接近价带边缘的位置。由于

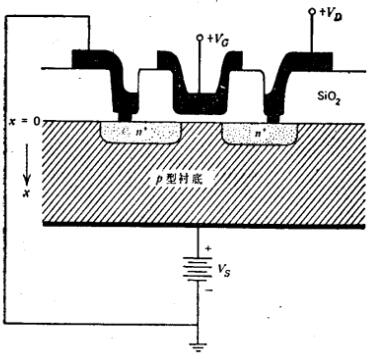

详解MOS管阈值电压-外加衬源偏压变化和影响因素,虽然MOS场效应晶体管常常是在联衬源相的情况下工作,并保持零电位,但考虑外加衬源电压对器件特性的影响也是相当重要的,衬源区之间的任何电位差对于MOS场效应晶体管电学参数的影响特别有趣,因为这种情况在集成电路中经常遇到。在集成电路中,许多单个元件的源区并不直接接地,在电路正常工作时,其电位相对于衬底而变化。图2.20表示一个在外加衬——源电压Vs,作

详解MOS管阈值电压-外加衬源偏压变化和影响因素,虽然MOS场效应晶体管常常是在联衬源相的情况下工作,并保持零电位,但考虑外加衬源电压对器件特性的影响也是相当重要的,衬源区之间的任何电位差对于MOS场效应晶体管电学参数的影响特别有趣,因为这种情况在集成电路中经常遇到。在集成电路中,许多单个元件的源区并不直接接地,在电路正常工作时,其电位相对于衬底而变化。图2.20表示一个在外加衬——源电压Vs,作