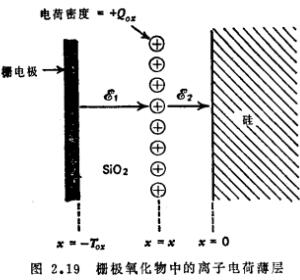

栅极绝缘物内离子电荷对MOS晶体管阈电压的影响,在推导MOS场效应晶体管阈电压表达式时,曾假定栅极氧化物所有电荷都是正的,非可动的,位置非常接近氧化物-硅界面。然而实际上,这并不总是完全正确。虽然栅极氧化物层内的离子电荷密度通常取正值,但是,其中可动的和非可动的都有,而且分布于整个氧化层。除非在制作MOS器件的过程中十分小心,否则栅极绝缘物就可能受到可动的正钠离子的污染,在外加栅极电压作用下,这些

栅极绝缘物内离子电荷对MOS晶体管阈电压的影响,在推导MOS场效应晶体管阈电压表达式时,曾假定栅极氧化物所有电荷都是正的,非可动的,位置非常接近氧化物-硅界面。然而实际上,这并不总是完全正确。虽然栅极氧化物层内的离子电荷密度通常取正值,但是,其中可动的和非可动的都有,而且分布于整个氧化层。除非在制作MOS器件的过程中十分小心,否则栅极绝缘物就可能受到可动的正钠离子的污染,在外加栅极电压作用下,这些

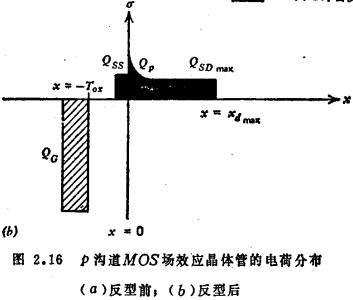

P沟道MOS管的阈电压,因为在阈电压方程内的-Qss,-QSDmax和+(фMS'+2фF)均取负值。因此,p沟道器件的阈电压始终为负,而与硅衬底受主掺杂浓度或Qss值无关。然而在需要p沟道MOS器件具有耗尽型特性的情况下,有几种技术可以使用。P沟道MOS管的阈电压。获得p沟道耗尽型器件使用最为广泛的方法是贯穿栅极绝缘物而对介于源漏之间的硅表面注入薄层受主杂质,由此提供一个介于两区之间甚至在零栅电

P沟道MOS管的阈电压,因为在阈电压方程内的-Qss,-QSDmax和+(фMS'+2фF)均取负值。因此,p沟道器件的阈电压始终为负,而与硅衬底受主掺杂浓度或Qss值无关。然而在需要p沟道MOS器件具有耗尽型特性的情况下,有几种技术可以使用。P沟道MOS管的阈电压。获得p沟道耗尽型器件使用最为广泛的方法是贯穿栅极绝缘物而对介于源漏之间的硅表面注入薄层受主杂质,由此提供一个介于两区之间甚至在零栅电

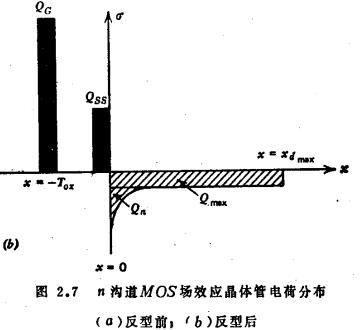

N沟道MOS管的阈值电压,N沟道MOS管的阈值电压,在平衡条件下,用均匀掺杂的p型硅衬底制作的具有二氧化硅栅极绝缘物的n沟道MOS场效应晶体管的电荷分布由图2.7所示。图2.7(a)表示低栅电压情况,这时在表面层只有耗尽区存在,耗尽区由延伸到x=xd的非可动离化受生构成。图2.7(b)表示栅极电压足够高而使p型衬底表面发生反型,形成一个n型反型层的情况。如前所述,当发生此类情况时,耗尽区将达到最大

N沟道MOS管的阈值电压,N沟道MOS管的阈值电压,在平衡条件下,用均匀掺杂的p型硅衬底制作的具有二氧化硅栅极绝缘物的n沟道MOS场效应晶体管的电荷分布由图2.7所示。图2.7(a)表示低栅电压情况,这时在表面层只有耗尽区存在,耗尽区由延伸到x=xd的非可动离化受生构成。图2.7(b)表示栅极电压足够高而使p型衬底表面发生反型,形成一个n型反型层的情况。如前所述,当发生此类情况时,耗尽区将达到最大

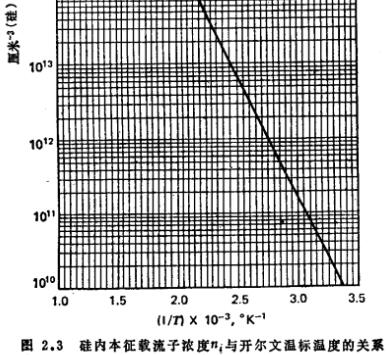

第二章 半导体表面的场效应2.1半导体表面附近的空间电荷区,可动载流子浓度和电场强度应用-维泊松方程的解,可以计算在外加垂直电场作用下半导体表面附近的空间电荷区、可动载流子浓度和电场强度之间的关系1。对于结构如图2.1所示的简单MOS电容器,假设x=0规定为硅-二氧化硅的界面,同时假设外加栅极电压的所有变化都足够缓慢,使整个系统总是处于热平衡状态,此时硅中的静电势 ф 与单位体积内总空间电荷密度ρ

第二章 半导体表面的场效应2.1半导体表面附近的空间电荷区,可动载流子浓度和电场强度应用-维泊松方程的解,可以计算在外加垂直电场作用下半导体表面附近的空间电荷区、可动载流子浓度和电场强度之间的关系1。对于结构如图2.1所示的简单MOS电容器,假设x=0规定为硅-二氧化硅的界面,同时假设外加栅极电压的所有变化都足够缓慢,使整个系统总是处于热平衡状态,此时硅中的静电势 ф 与单位体积内总空间电荷密度ρ

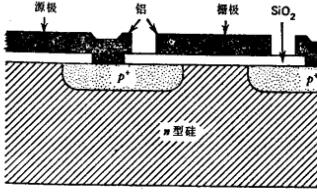

MOS管的工作基础原理,MOS场效应晶体管有两种不同的类型:n沟道MOS场效应晶体管是借横向外加电压影响下的电子表面电导来工作的;而在p沟道器件中引起电流的电荷载流子是空穴。对于相同的衬底掺杂浓度而言,硅中电子的迁移率明显地大于空穴的迁移率,因此,n沟道MOS晶体管的工作速度一般大于用类似方法制作的p沟道器件。p沟道MOS场效应晶体管的横截面见图1.1。器件包括两个间隔很近的简并掺杂p+区,即在轻

MOS管的工作基础原理,MOS场效应晶体管有两种不同的类型:n沟道MOS场效应晶体管是借横向外加电压影响下的电子表面电导来工作的;而在p沟道器件中引起电流的电荷载流子是空穴。对于相同的衬底掺杂浓度而言,硅中电子的迁移率明显地大于空穴的迁移率,因此,n沟道MOS晶体管的工作速度一般大于用类似方法制作的p沟道器件。p沟道MOS场效应晶体管的横截面见图1.1。器件包括两个间隔很近的简并掺杂p+区,即在轻

MOS集成电路从其结构上看,比双极型容易遭受破坏。使用MOS集成电路与使用高频晶体管一样,应加注意。图3.161给出各种破坏的例子。(1)栅破坏,氧化膜的绝缘耐压约为100V,如图3.16237)所示。烙铁漏电、电测量仪器的漏电,当然也会引起栅电极的静电破坏。目前对这种破坏采取了图3.162所示的各种保护措施,但使用时还应注意下述事项。①运输和保存时用铝箔或导电性容器密封起来。②工作时人体通过高电

MOS集成电路从其结构上看,比双极型容易遭受破坏。使用MOS集成电路与使用高频晶体管一样,应加注意。图3.161给出各种破坏的例子。(1)栅破坏,氧化膜的绝缘耐压约为100V,如图3.16237)所示。烙铁漏电、电测量仪器的漏电,当然也会引起栅电极的静电破坏。目前对这种破坏采取了图3.162所示的各种保护措施,但使用时还应注意下述事项。①运输和保存时用铝箔或导电性容器密封起来。②工作时人体通过高电

MOS集成电路的故障、MOS集成电路寿命方法,(1)统计处理,如欲逐一测量集成电路的寿命,在目前的技术条件下是不可能的。但可讨论一批集成电路的平均寿命。因此,统计处理极为重要。此处解释一下衡量可靠性的常用术语。可靠性:系统、机器或元件等在规定条件下,在一定的时间内能正确执行规定功能的几率33)。可靠性通常是与时间呈函数关系的几率,严格地说,它与表示一般概念的可靠性的意义不同。 可靠性函数R(t):

MOS集成电路的故障、MOS集成电路寿命方法,(1)统计处理,如欲逐一测量集成电路的寿命,在目前的技术条件下是不可能的。但可讨论一批集成电路的平均寿命。因此,统计处理极为重要。此处解释一下衡量可靠性的常用术语。可靠性:系统、机器或元件等在规定条件下,在一定的时间内能正确执行规定功能的几率33)。可靠性通常是与时间呈函数关系的几率,严格地说,它与表示一般概念的可靠性的意义不同。 可靠性函数R(t):

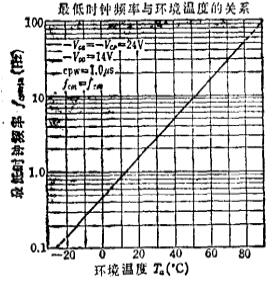

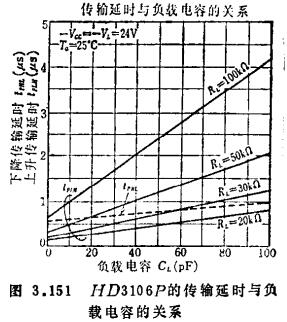

MOS集成电路检测、MOS集成电路注意事项,(1)MOS集成电路检测的一般注意事项 以往在购进晶体管、二极管等元件时,要判断这些元件是否能用于相应的电路。同样,集成电路出现后,则应判断是否能用这些集成电路构成系统。因此,作为购物基准的检测规格,与分立元件的情形相比要重要得多。使用集成电路的周围条件,例如电源电压、环境温度、负载条件等是变化的。这些条件之一或将这些条件组合起来处于最坏的状态,称为最坏

MOS集成电路检测、MOS集成电路注意事项,(1)MOS集成电路检测的一般注意事项 以往在购进晶体管、二极管等元件时,要判断这些元件是否能用于相应的电路。同样,集成电路出现后,则应判断是否能用这些集成电路构成系统。因此,作为购物基准的检测规格,与分立元件的情形相比要重要得多。使用集成电路的周围条件,例如电源电压、环境温度、负载条件等是变化的。这些条件之一或将这些条件组合起来处于最坏的状态,称为最坏

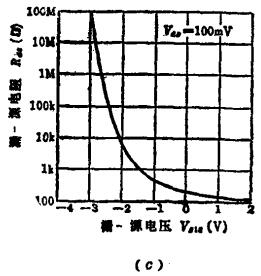

MOS晶体管的检测、MOS晶体管的测量、MOS晶体管输出入特性同其它四端器件一样,亦有输入特性、转移特性、输出特性等特性。现以N沟道耗尽型斩波器用的MOS场效应晶体管3SK21日为例说明检测方法(参见表3.21)。测量栅漏泄电流相当于测量氧化层绝缘膜的漏泄电阻(6Ⅹ1012Ω以上),应完全在静电屏蔽的条件下进行,场效应晶体管管座玻璃的外表面漏电也有图3.137那样的问题。

MOS晶体管的检测、MOS晶体管的测量、MOS晶体管输出入特性同其它四端器件一样,亦有输入特性、转移特性、输出特性等特性。现以N沟道耗尽型斩波器用的MOS场效应晶体管3SK21日为例说明检测方法(参见表3.21)。测量栅漏泄电流相当于测量氧化层绝缘膜的漏泄电阻(6Ⅹ1012Ω以上),应完全在静电屏蔽的条件下进行,场效应晶体管管座玻璃的外表面漏电也有图3.137那样的问题。

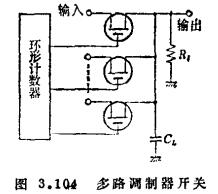

MOS模拟开关、MOS模拟电路、MOS数字微分分析器对模拟信号作取样保持,或电子计算机、自动控制机等机器中变换多数信号时所用的开关,都是模拟开关。模拟开关不只是像斩波器那样使微弱信号通断,而且能用作较大信号的开关。MOS模拟开关的主要用途有1)比较器2)电子计算机的分时处理3)遥测仪的分时传输4)取样保持电路、模拟存储器等等。

MOS模拟开关、MOS模拟电路、MOS数字微分分析器对模拟信号作取样保持,或电子计算机、自动控制机等机器中变换多数信号时所用的开关,都是模拟开关。模拟开关不只是像斩波器那样使微弱信号通断,而且能用作较大信号的开关。MOS模拟开关的主要用途有1)比较器2)电子计算机的分时处理3)遥测仪的分时传输4)取样保持电路、模拟存储器等等。