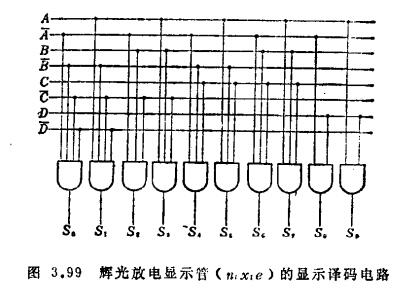

显示电路属于串行同步式计算机中的台式机所用的显示电路系统,如图3.97所示,是将各位显示时间错开进行显示的扫描显示方式25)。因而,通常只显示1位,具有低功耗和构成元件少等特点。所用器件有暂存二进制数码的移位寄存器、转变为十进制数的译码器以及规定显示数位的数字计数器。因数字计数器可由前节所述的定时脉冲发生电路构成,此处只谈译码器及其驱动电路。(1)辉光放电管显示电路及其驱动电路辉光放电管因其特性要

显示电路属于串行同步式计算机中的台式机所用的显示电路系统,如图3.97所示,是将各位显示时间错开进行显示的扫描显示方式25)。因而,通常只显示1位,具有低功耗和构成元件少等特点。所用器件有暂存二进制数码的移位寄存器、转变为十进制数的译码器以及规定显示数位的数字计数器。因数字计数器可由前节所述的定时脉冲发生电路构成,此处只谈译码器及其驱动电路。(1)辉光放电管显示电路及其驱动电路辉光放电管因其特性要

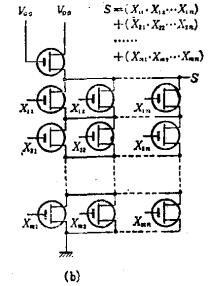

MOS集成控制电路这种电路是控制计算机的电路,换句话说,是为了对计算处理进行程序控制,将功能信号译成二进制数码,并发出串行编码的指令信号的电路。譬如,在进行乘法运算时,按照图3.92的操作程序图发出移位指令、转移指令、判断指令、加法指令和计数指令等,并将这些指令串行编码24)。由MOS集成电路满足这类功能的电路有如下几种。(1)由随机门构成的控制电路控制电路一般由“与-或”门组成,由于信息信号能够

MOS集成控制电路这种电路是控制计算机的电路,换句话说,是为了对计算处理进行程序控制,将功能信号译成二进制数码,并发出串行编码的指令信号的电路。譬如,在进行乘法运算时,按照图3.92的操作程序图发出移位指令、转移指令、判断指令、加法指令和计数指令等,并将这些指令串行编码24)。由MOS集成电路满足这类功能的电路有如下几种。(1)由随机门构成的控制电路控制电路一般由“与-或”门组成,由于信息信号能够

MOS定时脉冲电路,台式电子计算机主要是串行同步式计算机,其中不可缺少的定时脉冲发生电路是规定信息流动的时间位置,对计算机进行时间分配的电路,它用来控制运算、存贮、显示等的驱动。换句话说,是构成计算机的中枢电路。此种电路以振荡器发生的方波脉冲作为信号源,确定时间位置的时钟脉冲,表示二进制数的位的t1、t2、t4、t8,表示十进制数n位的等是其产生的输出信号。图3.81给出计算机时间分配定时脉冲的一

MOS定时脉冲电路,台式电子计算机主要是串行同步式计算机,其中不可缺少的定时脉冲发生电路是规定信息流动的时间位置,对计算机进行时间分配的电路,它用来控制运算、存贮、显示等的驱动。换句话说,是构成计算机的中枢电路。此种电路以振荡器发生的方波脉冲作为信号源,确定时间位置的时钟脉冲,表示二进制数的位的t1、t2、t4、t8,表示十进制数n位的等是其产生的输出信号。图3.81给出计算机时间分配定时脉冲的一

本节将要叙述实际存储器如何构成。在构成存储器时,外围电路有使用MOS电路和使用双极型电路的两种情形,本节只讲使用MOS电路的情形。(1)MOS存储器 由于MOS电路容易集成并且功耗低,如充分利用这些特点即可在单片上制造全部存储单元和外围电路。从这种意义上来说,希望对MOS存储单元使用MOS外围电路。但考虑到速度等因素时,MOS外围电路就不一定能充分满足要求。

本节将要叙述实际存储器如何构成。在构成存储器时,外围电路有使用MOS电路和使用双极型电路的两种情形,本节只讲使用MOS电路的情形。(1)MOS存储器 由于MOS电路容易集成并且功耗低,如充分利用这些特点即可在单片上制造全部存储单元和外围电路。从这种意义上来说,希望对MOS存储单元使用MOS外围电路。但考虑到速度等因素时,MOS外围电路就不一定能充分满足要求。

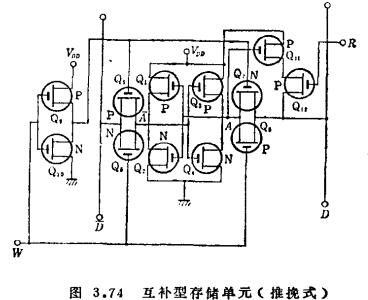

MOS存储器发挥其大容量的特点,被广泛地用于电子计算机的主存领域。本节将说明MOS被用于何种存储器,具有何种电路形式?下一节叙述实际构成存储器的方法。(1)MOS存储单元用只有P沟道(或N沟道)的单一沟道MOS构成的存储单元的例子,如图3.72所示。Q1~Q4构成触发器,Q5、Q6用用于线选通,在写入“1”时,向位线D输进正脉冲。向地址线上输进负脉冲,可使Q5导通,Q2截止。另外藉助

MOS存储器发挥其大容量的特点,被广泛地用于电子计算机的主存领域。本节将说明MOS被用于何种存储器,具有何种电路形式?下一节叙述实际构成存储器的方法。(1)MOS存储单元用只有P沟道(或N沟道)的单一沟道MOS构成的存储单元的例子,如图3.72所示。Q1~Q4构成触发器,Q5、Q6用用于线选通,在写入“1”时,向位线D输进正脉冲。向地址线上输进负脉冲,可使Q5导通,Q2截止。另外藉助

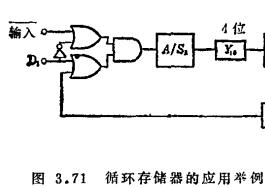

MOS移位寄存器的功能和应用,移位寄存器的功能大体上可分为作为延迟电路的功能和作为循环存储器的功能。前者是使信号延迟任意位(时间)的除移位寄存器外,还有磁致伸缩线等。后者是用时钟脉冲不断使信号移位并使之循环,以保持数据的存储。此处以台式计算机为例,叙述移位寄存器的使用方法。首先列举一个存储操作指令及相伴的判断指令的电路。此电路有一位静态型移位寄存器。

MOS移位寄存器的功能和应用,移位寄存器的功能大体上可分为作为延迟电路的功能和作为循环存储器的功能。前者是使信号延迟任意位(时间)的除移位寄存器外,还有磁致伸缩线等。后者是用时钟脉冲不断使信号移位并使之循环,以保持数据的存储。此处以台式计算机为例,叙述移位寄存器的使用方法。首先列举一个存储操作指令及相伴的判断指令的电路。此电路有一位静态型移位寄存器。

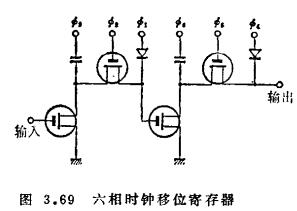

MOS移位寄存器的种类(静态型、动态型、 多相时钟)大体上可分为静态静型和动态型两种。态型移位寄存器过去由双极型集成电路等构成的J-K触发器组成。动态型主要利用MOS集成电路特有的栅电容暂存信息的功能,属于用两相时钟转移信息的类型。除了用两相时钟移位外,为了降低功耗,也有增加时钟数目、用多相时钟转移信息的电路。这些电路的工作原理以后再说明。(1)静态型移位寄存器静态型移位寄存器典型的电路例子

MOS移位寄存器的种类(静态型、动态型、 多相时钟)大体上可分为静态静型和动态型两种。态型移位寄存器过去由双极型集成电路等构成的J-K触发器组成。动态型主要利用MOS集成电路特有的栅电容暂存信息的功能,属于用两相时钟转移信息的类型。除了用两相时钟移位外,为了降低功耗,也有增加时钟数目、用多相时钟转移信息的电路。这些电路的工作原理以后再说明。(1)静态型移位寄存器静态型移位寄存器典型的电路例子

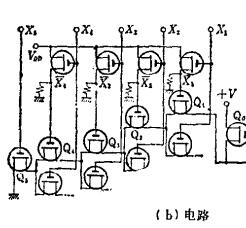

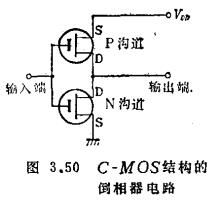

C-MOS逻辑电路.C-MOS(互补MOS)逻辑电路,C-MOS(互补MOS)逻辑电路以上各节叙述了单一沟道(P沟道或N沟道)MOS晶体管逻辑电路。此处对P沟道和N沟道组成的C-MOS结构的逻辑电路加以说明。该电路中,将P沟道晶体管的漏与N沟道晶体管的漏接在一起作为输出端,将两个晶体管的栅接在一起作为输入端。并且在P沟道的源上加正电压,在N沟道的源上加负电压。若在输入端加电压,当Vin=0时,P沟

C-MOS逻辑电路.C-MOS(互补MOS)逻辑电路,C-MOS(互补MOS)逻辑电路以上各节叙述了单一沟道(P沟道或N沟道)MOS晶体管逻辑电路。此处对P沟道和N沟道组成的C-MOS结构的逻辑电路加以说明。该电路中,将P沟道晶体管的漏与N沟道晶体管的漏接在一起作为输出端,将两个晶体管的栅接在一起作为输入端。并且在P沟道的源上加正电压,在N沟道的源上加负电压。若在输入端加电压,当Vin=0时,P沟

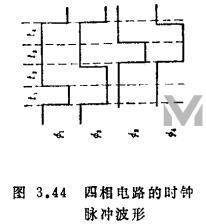

MOS集成电路多用两相时钟的电路方式,三相、四相等多相时钟电路也在进行研究。此处简单介绍大家最熟悉的多相时钟电路即四相时钟方式的逻辑电路。图3.43给出该电路的基本门电路,根据应加到端点的时钟信号可分为四类。图3.44表示出应加的时钟信号。在说明电路时.设所用的晶体管处于低电平L时为导通状态;处于高电平H时为截止状态。现以图3.43的第二类电路为例进行说明。

MOS集成电路多用两相时钟的电路方式,三相、四相等多相时钟电路也在进行研究。此处简单介绍大家最熟悉的多相时钟电路即四相时钟方式的逻辑电路。图3.43给出该电路的基本门电路,根据应加到端点的时钟信号可分为四类。图3.44表示出应加的时钟信号。在说明电路时.设所用的晶体管处于低电平L时为导通状态;处于高电平H时为截止状态。现以图3.43的第二类电路为例进行说明。

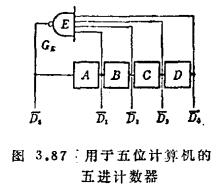

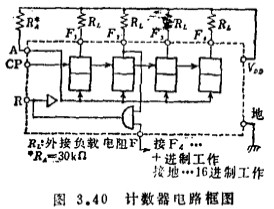

MOS集成计数器电路图工作原理前节的二进制触发器电路,输入一组“0”“1”的脉冲,也就是输入一位输入脉冲之后,输出才翻转。因此,可以得到重复1/2输入周期的输出。从而当这些触发器电路级联时,可以构成二进制计数电路,该电路从初级起各级具有20、21,22、…2n的二进制编码权。设输入脉冲的频率为fi,级联的级数为n,则最末级输出脉冲的重复频率为,为了得到任意的n进制计数电路,可向前级加反馈。在连成n

MOS集成计数器电路图工作原理前节的二进制触发器电路,输入一组“0”“1”的脉冲,也就是输入一位输入脉冲之后,输出才翻转。因此,可以得到重复1/2输入周期的输出。从而当这些触发器电路级联时,可以构成二进制计数电路,该电路从初级起各级具有20、21,22、…2n的二进制编码权。设输入脉冲的频率为fi,级联的级数为n,则最末级输出脉冲的重复频率为,为了得到任意的n进制计数电路,可向前级加反馈。在连成n