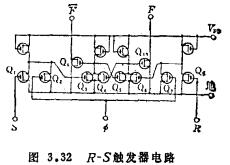

MOS集成触发器电路,在各种控制仪器和台式电子计算机等设备中,使用了各种MOS集成电路的触发器电路,它们可分为四类。(1)R-S触发器电路和R-S-S触发器电路,R-S触发器电路的真值表如表3.8所示。当置位(S)、复位(R)均为“L”,时钟(ф )亦为“L”时,输出处于保持状态;时钟ф 为“H”时,S、R输入是有效的,与ф 同步变化。但S、R均为H时,输出状态不能唯一确定,所以是“禁止”状态。

MOS集成触发器电路,在各种控制仪器和台式电子计算机等设备中,使用了各种MOS集成电路的触发器电路,它们可分为四类。(1)R-S触发器电路和R-S-S触发器电路,R-S触发器电路的真值表如表3.8所示。当置位(S)、复位(R)均为“L”,时钟(ф )亦为“L”时,输出处于保持状态;时钟ф 为“H”时,S、R输入是有效的,与ф 同步变化。但S、R均为H时,输出状态不能唯一确定,所以是“禁止”状态。

门电路可认为是倒相器电路的变形,基本上有图3.26所示的串联方式和并联方式。图(a)的电路为二输入端“或非”门(正逻辑)或为“与非”门(负逻辑)。一般,在这种电路方式中输出电压取决于两驱动管Q2、Q3导通电阻之和,为了得到与图(b)电路的相同特性,必须增加晶体管的面积,提高其跨导gm。这样做很不经济。所以实例很少。图(b)的电路为二输入端“与非”门(正逻辑)或为“或非”门(负逻辑)。MOS集成门电

门电路可认为是倒相器电路的变形,基本上有图3.26所示的串联方式和并联方式。图(a)的电路为二输入端“或非”门(正逻辑)或为“与非”门(负逻辑)。一般,在这种电路方式中输出电压取决于两驱动管Q2、Q3导通电阻之和,为了得到与图(b)电路的相同特性,必须增加晶体管的面积,提高其跨导gm。这样做很不经济。所以实例很少。图(b)的电路为二输入端“与非”门(正逻辑)或为“或非”门(负逻辑)。MOS集成门电

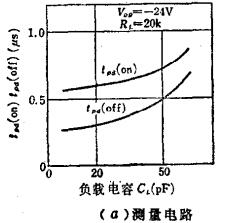

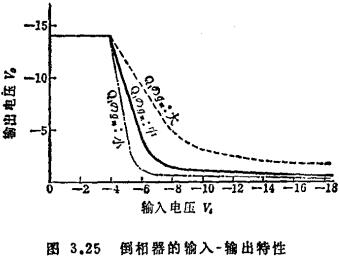

MOS集成倒相器电路,现在对所有电路的基础——倒相器加以说明,作为应用MOS集成电路的例子。为便于说明起见,设晶体管的形式为P沟道增强型,电压电平用正逻辑。倒相器电路由跨导gm互不相同的两个晶体管Q1、Q2串联组成,因系集成电路,使用同一衬底,如图3.23所示。负载管Q1的栅上所加电压有VGG=VDD的情形,也有|VGG|>|VDD+Vth|的情形。前一种MOS负载管的工作状态为饱和型,此处除非特

MOS集成倒相器电路,现在对所有电路的基础——倒相器加以说明,作为应用MOS集成电路的例子。为便于说明起见,设晶体管的形式为P沟道增强型,电压电平用正逻辑。倒相器电路由跨导gm互不相同的两个晶体管Q1、Q2串联组成,因系集成电路,使用同一衬底,如图3.23所示。负载管Q1的栅上所加电压有VGG=VDD的情形,也有|VGG|>|VDD+Vth|的情形。前一种MOS负载管的工作状态为饱和型,此处除非特

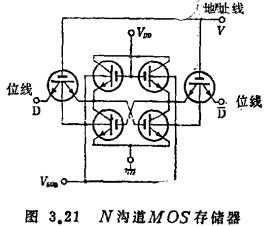

MOS集成设计基本电路举例,图3.20是由P沟道晶体管构成的“或非”门电路。该电路采用漏接地的形式,备有输出缓冲器。大规模集成电路中的电路也常用这种门电路来组合。N沟道144位存储器是作为高速MOS存储器研制的18),用于该存储器的单元电路如图3.21所示。它是由触发器和写入一读出门构成的简单电路,为了实现40毫微秒的高速度的写入时间,我们采用迁移率高的N沟道。由于用通常工艺做出的MOS管为耗尽型

MOS集成设计基本电路举例,图3.20是由P沟道晶体管构成的“或非”门电路。该电路采用漏接地的形式,备有输出缓冲器。大规模集成电路中的电路也常用这种门电路来组合。N沟道144位存储器是作为高速MOS存储器研制的18),用于该存储器的单元电路如图3.21所示。它是由触发器和写入一读出门构成的简单电路,为了实现40毫微秒的高速度的写入时间,我们采用迁移率高的N沟道。由于用通常工艺做出的MOS管为耗尽型

MOS大规模集成化的优点,除了3.2.1节所述的一般优点外,还有下列优点。与双极型晶体管相比;MOS晶体管的制造工艺简单,而且仅用同一种元件就可实现复杂的功能,所以MOS大规模集成电路成品率高,有利于大规模集成化。MOS大规模集成化。由于MOS集成电路的阻抗高,可以藉助与源、漏扩散区同时制作的穿接区,实现立体交叉布线而不影响电路的直流特性。因此,在需要作复杂布线时,也毋须使用会影响成品率的高难度技

MOS大规模集成化的优点,除了3.2.1节所述的一般优点外,还有下列优点。与双极型晶体管相比;MOS晶体管的制造工艺简单,而且仅用同一种元件就可实现复杂的功能,所以MOS大规模集成电路成品率高,有利于大规模集成化。MOS大规模集成化。由于MOS集成电路的阻抗高,可以藉助与源、漏扩散区同时制作的穿接区,实现立体交叉布线而不影响电路的直流特性。因此,在需要作复杂布线时,也毋须使用会影响成品率的高难度技

MOS集成电路的设计与作为分立元件的MOS晶体管的设计不同,集成电路内部的杂散电容小,为了得到一定的速度,gm可以做得很小,可以使晶体管的面积做得很小;同时集成电路的元件之间必需隔离。MOS集成电路设计要点。关于隔离的问题,如图3.19所示,若氧化膜跨过两个扩散层穿接区,在氧化膜上又有金属布线时,相当于在该处构成了一个MOS晶体管,在集成电路中意识不到的部分可能产生晶体管的作用。象这样的由布线等原

MOS集成电路的设计与作为分立元件的MOS晶体管的设计不同,集成电路内部的杂散电容小,为了得到一定的速度,gm可以做得很小,可以使晶体管的面积做得很小;同时集成电路的元件之间必需隔离。MOS集成电路设计要点。关于隔离的问题,如图3.19所示,若氧化膜跨过两个扩散层穿接区,在氧化膜上又有金属布线时,相当于在该处构成了一个MOS晶体管,在集成电路中意识不到的部分可能产生晶体管的作用。象这样的由布线等原

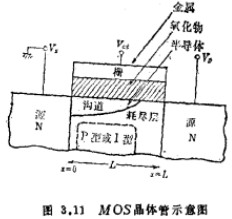

MOS集成电路的功能,放大MOS晶体管作为有源元件,本来就是用作放大元件的。在图3.15所示的互补型电路中,P沟道和N沟道晶体管互为有源元件和负载元件而工作,适用于重负载驱动和小功率电路。但与单沟道MOS集成电路相比,工艺流程复杂。(2)负载考虑其控制参数和芯片面积等单项功能,用MOS晶体管做负载要比扩散电阻负载有利。MOS晶体管负载利用了漏-源间的伏安特性,依栅接地的形式大体分为两

MOS集成电路的功能,放大MOS晶体管作为有源元件,本来就是用作放大元件的。在图3.15所示的互补型电路中,P沟道和N沟道晶体管互为有源元件和负载元件而工作,适用于重负载驱动和小功率电路。但与单沟道MOS集成电路相比,工艺流程复杂。(2)负载考虑其控制参数和芯片面积等单项功能,用MOS晶体管做负载要比扩散电阻负载有利。MOS晶体管负载利用了漏-源间的伏安特性,依栅接地的形式大体分为两

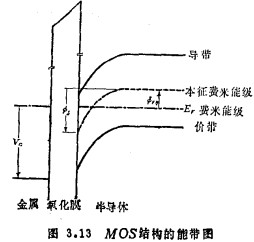

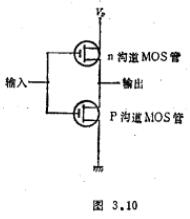

MOS晶体管特性集成电路是由晶体管组合而成的,因而在集成电路设计中希望单个晶体管的特性简单。为此,多采用粗略近似的简单表达式。其要点如下。这类简单的表达式之一是,流过MOS品体管的电流有与饱和区有效栅电压的平方成正比1)的关系。这一关系基于这样的事实;当半导体内感生的载流子电荷Qs与有效栅电压成正比,漏电压在源端产生的电场也与有效栅电压成正比时,特性曲线趋于饱和。关于电流的另一近似是漂移电荷的速度

MOS晶体管特性集成电路是由晶体管组合而成的,因而在集成电路设计中希望单个晶体管的特性简单。为此,多采用粗略近似的简单表达式。其要点如下。这类简单的表达式之一是,流过MOS品体管的电流有与饱和区有效栅电压的平方成正比1)的关系。这一关系基于这样的事实;当半导体内感生的载流子电荷Qs与有效栅电压成正比,漏电压在源端产生的电场也与有效栅电压成正比时,特性曲线趋于饱和。关于电流的另一近似是漂移电荷的速度

MOS晶体管集成电路结构举例,图3.12给出N沟道MOS存储器大规模集成电路的局部放大照片及与之对应的排布图形。这一部分大致包括存储器触发器电路的一半。最下面看到一半的是放大晶体管,它上面是进行写入和读出的位晶体管,右上角为电源VDD。左侧为负载晶体管。现以位于中心部分的位晶体管来说明晶体管的构成方法。N型扩散区用单斜线表示,配置在上下两方。上侧的扩散区为该位晶体管专用;下侧的扩散区与放大晶体管的

MOS晶体管集成电路结构举例,图3.12给出N沟道MOS存储器大规模集成电路的局部放大照片及与之对应的排布图形。这一部分大致包括存储器触发器电路的一半。最下面看到一半的是放大晶体管,它上面是进行写入和读出的位晶体管,右上角为电源VDD。左侧为负载晶体管。现以位于中心部分的位晶体管来说明晶体管的构成方法。N型扩散区用单斜线表示,配置在上下两方。上侧的扩散区为该位晶体管专用;下侧的扩散区与放大晶体管的

MOS集成大规模集成电路设计,一般的趋势是,集成电路的集成度越高,集成电路功能方面的自由度就越少。另一方面,因为大规模集成电路需要大量研制经费,所以应尽量多生产同一种电路,提高其批量生产的经济效果。解决这两者的矛盾,是大规模集成电路的一个大课题。在大规模集成电路产品化的早期,这个问题主要表现在系统分割上,即一个系统用几块大规模集成电路构成时,对该系统如何分割才能提高各大规模集成电路功能的自由度的问

MOS集成大规模集成电路设计,一般的趋势是,集成电路的集成度越高,集成电路功能方面的自由度就越少。另一方面,因为大规模集成电路需要大量研制经费,所以应尽量多生产同一种电路,提高其批量生产的经济效果。解决这两者的矛盾,是大规模集成电路的一个大课题。在大规模集成电路产品化的早期,这个问题主要表现在系统分割上,即一个系统用几块大规模集成电路构成时,对该系统如何分割才能提高各大规模集成电路功能的自由度的问