自对准栅极MOS场效应晶体管和集成电路,通常制作增强型MOS场效应晶体管和MOS集成电路的技术要求栅电极的长度稍大于漏-源之间的间距。这个要求是基于这样的事实,即在漏源区扩散进入硅衬底之后,通常必须使栅电极与漏区和源区对准。任何偏差都会因栅极不能完全复盖两个扩散区之间的区域而使器件失效。栅电极的设计长度稍大于漏源间距,虽然可以消除因为栅极对不准而引起的器件失效,但是由于栅电极与漏-源扩散区重迭所引

自对准栅极MOS场效应晶体管和集成电路,通常制作增强型MOS场效应晶体管和MOS集成电路的技术要求栅电极的长度稍大于漏-源之间的间距。这个要求是基于这样的事实,即在漏源区扩散进入硅衬底之后,通常必须使栅电极与漏区和源区对准。任何偏差都会因栅极不能完全复盖两个扩散区之间的区域而使器件失效。栅电极的设计长度稍大于漏源间距,虽然可以消除因为栅极对不准而引起的器件失效,但是由于栅电极与漏-源扩散区重迭所引

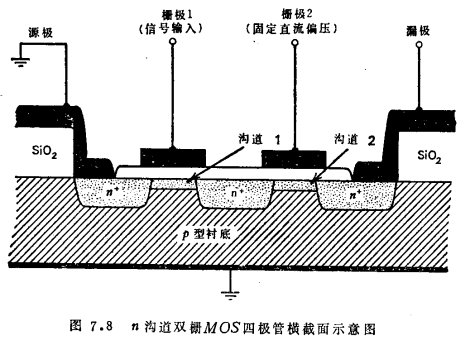

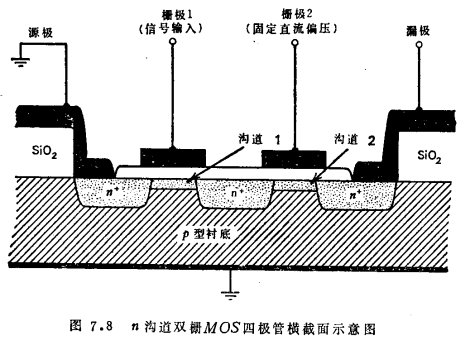

双栅极MOS四极管结构可以消除普通的MOS场效应晶体管所固有的栅-漏之间的相当可观的负反馈电容。如同偏置栅极器件一样,双栅极四极管的设计是用增大引进输入信号的栅电极和漏电极之间的实际间距的办法来减小CGD电容,从而取得稳定的高频运用。输入信号加在四极管栅极1上,而在栅极2上所加的固定直流电压可以控制沟道2形成的输入和输出之间的可变阻抗缓冲作用的大小。位于四极管中心的n+区仅用作两个沟道之间的导线。

双栅极MOS四极管结构可以消除普通的MOS场效应晶体管所固有的栅-漏之间的相当可观的负反馈电容。如同偏置栅极器件一样,双栅极四极管的设计是用增大引进输入信号的栅电极和漏电极之间的实际间距的办法来减小CGD电容,从而取得稳定的高频运用。输入信号加在四极管栅极1上,而在栅极2上所加的固定直流电压可以控制沟道2形成的输入和输出之间的可变阻抗缓冲作用的大小。位于四极管中心的n+区仅用作两个沟道之间的导线。

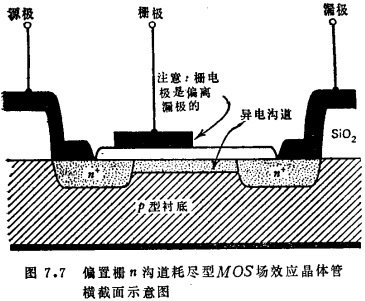

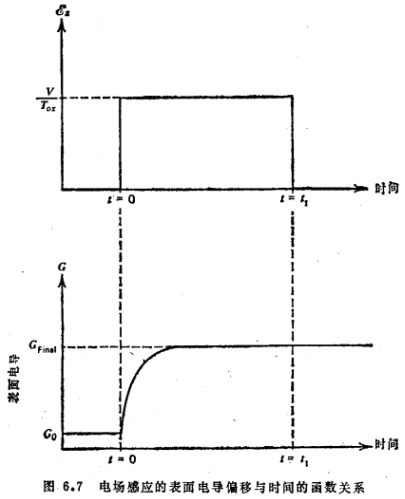

解析偏置栅极N沟道耗尽型MOS场效应晶体管结构特性。虽然,对于增强型器件,要求栅电极完全覆盖在漏-源之间的间隙上面,但是对于耗尽型MOS场效应晶体管却无此必要。如果在漏源之间存在着导电表面沟道,则这两个区之间的电流会受到如图7.7所示的n沟道MOS场效应晶体管偏置绝缘栅结构的调节。因为使栅电极偏置远离漏极,负反馈电容CGD将大为减小,但是由于漏区附近沟道的未调部分,势必引进很小的串联电阻。虽然在外

解析偏置栅极N沟道耗尽型MOS场效应晶体管结构特性。虽然,对于增强型器件,要求栅电极完全覆盖在漏-源之间的间隙上面,但是对于耗尽型MOS场效应晶体管却无此必要。如果在漏源之间存在着导电表面沟道,则这两个区之间的电流会受到如图7.7所示的n沟道MOS场效应晶体管偏置绝缘栅结构的调节。因为使栅电极偏置远离漏极,负反馈电容CGD将大为减小,但是由于漏区附近沟道的未调部分,势必引进很小的串联电阻。虽然在外

对于发展绝缘栅场效应晶体管结构作了大量的研究工作,这种结构与普通的p沟道硅MOS场效应晶体管比较,工作频率更高。因为提高跨导与有源沟道电容之比和消除与器件结构有关的所有寄生电容就能提高绝缘栅场效应晶体管的最高工作频率,一般在三个方面做出了努力:1、对绝缘栅场效应晶体管设法采用高迁移率衬底材料。2、通过应用自对准栅极的绝缘栅场效应晶体管结构,设法使沟道长度短的器件的寄生栅-漏和栅-源电容减到最小。3

对于发展绝缘栅场效应晶体管结构作了大量的研究工作,这种结构与普通的p沟道硅MOS场效应晶体管比较,工作频率更高。因为提高跨导与有源沟道电容之比和消除与器件结构有关的所有寄生电容就能提高绝缘栅场效应晶体管的最高工作频率,一般在三个方面做出了努力:1、对绝缘栅场效应晶体管设法采用高迁移率衬底材料。2、通过应用自对准栅极的绝缘栅场效应晶体管结构,设法使沟道长度短的器件的寄生栅-漏和栅-源电容减到最小。3

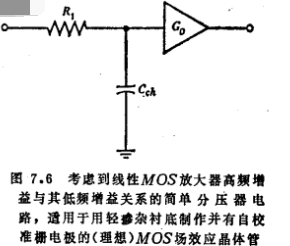

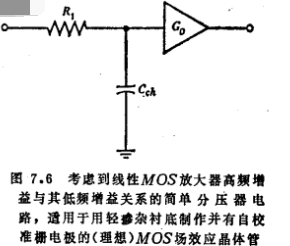

MOS场效应晶体管渡越时间的考虑及工作频率解析对于用轻掺杂衬底制作并有完全自对准的绝缘栅场效应晶体管,它的寄生栅-漏,栅-源和漏-衬电容影响可以忽略不计,器件最高工作频率受载流子从源区运动到漏区的渡越时间的限制。在这样的条件下,最大工作频率等于式中,渡越时间t等于现在,当晶体管在夹断点以下工作时,V等于漏电压VD。然而,当器件在饱和漏电流区的夹断点以上工作时,VG-VT将加在沟道上,VD-(VG-

MOS场效应晶体管渡越时间的考虑及工作频率解析对于用轻掺杂衬底制作并有完全自对准的绝缘栅场效应晶体管,它的寄生栅-漏,栅-源和漏-衬电容影响可以忽略不计,器件最高工作频率受载流子从源区运动到漏区的渡越时间的限制。在这样的条件下,最大工作频率等于式中,渡越时间t等于现在,当晶体管在夹断点以下工作时,V等于漏电压VD。然而,当器件在饱和漏电流区的夹断点以上工作时,VG-VT将加在沟道上,VD-(VG-

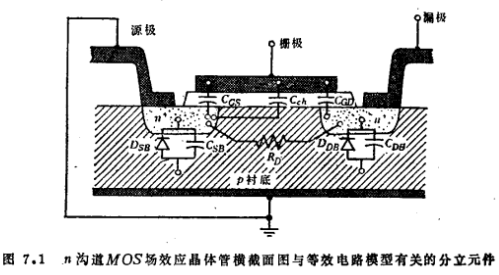

由考察MOS场效应晶体管的结构发现,器件的物理性质可以概括为由分立元件构成的等效电路。而这个等效电路又可以用来预测随频率而变的MOS场效应晶体管的特性1。图7-1表示一个典型的(n沟道)MOS场效应晶体管的横截面图。在物理性质上与结构每一部分有关的各个分立元件也在对应的区域表示于图中。用来表示各分立组件的符号规定如下:CCh=栅电极对有源沟道区的电容。CDb=随漏-衬电势而变的漏-衬结电容。CSB

由考察MOS场效应晶体管的结构发现,器件的物理性质可以概括为由分立元件构成的等效电路。而这个等效电路又可以用来预测随频率而变的MOS场效应晶体管的特性1。图7-1表示一个典型的(n沟道)MOS场效应晶体管的横截面图。在物理性质上与结构每一部分有关的各个分立元件也在对应的区域表示于图中。用来表示各分立组件的符号规定如下:CCh=栅电极对有源沟道区的电容。CDb=随漏-衬电势而变的漏-衬结电容。CSB

普通MOS场效应晶体管和集成电路的速度限制一般来说,与普通的硅MOS场效应晶体管比较,硅双极型晶体管能够在高得多的频率下工作。MOS场效应晶体管工作速度相对较低,其中一个主要原因是存在颇为可观的栅-漏电容。对于增强型器件,因为在栅-源电压为零时,并不存在原始沟道,栅电极必须完全覆盖漏-源之间的间隙,这样,当施加适当极性的栅极电压时,在这两区之间可以形成导电沟道。栅电极的设计通常是使它和漏及源电极略

普通MOS场效应晶体管和集成电路的速度限制一般来说,与普通的硅MOS场效应晶体管比较,硅双极型晶体管能够在高得多的频率下工作。MOS场效应晶体管工作速度相对较低,其中一个主要原因是存在颇为可观的栅-漏电容。对于增强型器件,因为在栅-源电压为零时,并不存在原始沟道,栅电极必须完全覆盖漏-源之间的间隙,这样,当施加适当极性的栅极电压时,在这两区之间可以形成导电沟道。栅电极的设计通常是使它和漏及源电极略

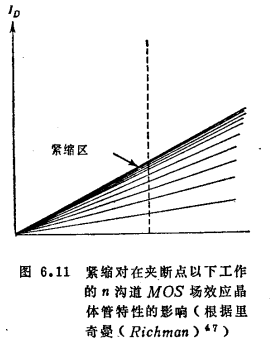

MOS场效应晶体管表面迁移率随外加漏极电压的变化,虽然一级理论预计MOS场效应晶体管的跨导与扩散漏区和源区之间的间距成正比,但是,在沟道长度很短时,这种关系不再成立,事实上,硅器件单位沟道宽度的跨导趋向一个极限值,因为在非常高的横向电场作用下,沟道内载流子的迁移率在给定的栅极电压下不再是常数,而开始随横向电场强度的增加而减小。电场强度超过临界值时,载流子漂移速度趋向饱和,所观测到的载流子迁移率随电

MOS场效应晶体管表面迁移率随外加漏极电压的变化,虽然一级理论预计MOS场效应晶体管的跨导与扩散漏区和源区之间的间距成正比,但是,在沟道长度很短时,这种关系不再成立,事实上,硅器件单位沟道宽度的跨导趋向一个极限值,因为在非常高的横向电场作用下,沟道内载流子的迁移率在给定的栅极电压下不再是常数,而开始随横向电场强度的增加而减小。电场强度超过临界值时,载流子漂移速度趋向饱和,所观测到的载流子迁移率随电

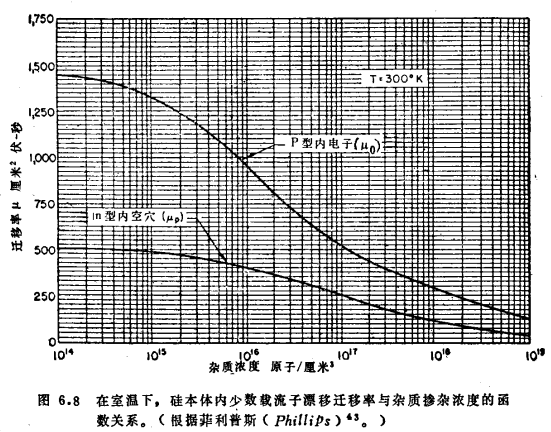

MOS场效应晶体管由于(6.4)式内有附加表面散射项,发现穿过MOS场效应晶体管的沟道区的载流子迁移率比半导体本体内的迁移率要低。(在室温下硅本体内电子和空穴迁移率的数值作为衬底掺杂浓度的函数已由菲利普斯(Phillips)43作出如图6.8的图表。)如前节所讨论的,随着栅极电压的增加,载流子的有效迁移率进一步下降。在Vc值低时,迁移率下降非常小,但是当栅极电压数值增加时,影响迅速增长44-48。

MOS场效应晶体管由于(6.4)式内有附加表面散射项,发现穿过MOS场效应晶体管的沟道区的载流子迁移率比半导体本体内的迁移率要低。(在室温下硅本体内电子和空穴迁移率的数值作为衬底掺杂浓度的函数已由菲利普斯(Phillips)43作出如图6.8的图表。)如前节所讨论的,随着栅极电压的增加,载流子的有效迁移率进一步下降。在Vc值低时,迁移率下降非常小,但是当栅极电压数值增加时,影响迅速增长44-48。

通过绝缘栅MOS场效应晶体管的电流与沟道区内电源区向漏区移动的载流子的有效迁移率成正比。在推导描述MOS器件电特性的方程时一般假定沟道内载流子的迁移率等于常数,与外加栅-漏电压无关。虽然这对典型的MOS场效应晶体管在一级近似内能很好地成立,但是,已经证明,当器件在较大的外加栅极电压下工作时以及当器件的沟道长度很短并在较大的外加漏极电压下工作时,载流子迁移率为常数的假设就不能成立了。此外,表示沟道内

通过绝缘栅MOS场效应晶体管的电流与沟道区内电源区向漏区移动的载流子的有效迁移率成正比。在推导描述MOS器件电特性的方程时一般假定沟道内载流子的迁移率等于常数,与外加栅-漏电压无关。虽然这对典型的MOS场效应晶体管在一级近似内能很好地成立,但是,已经证明,当器件在较大的外加栅极电压下工作时以及当器件的沟道长度很短并在较大的外加漏极电压下工作时,载流子迁移率为常数的假设就不能成立了。此外,表示沟道内