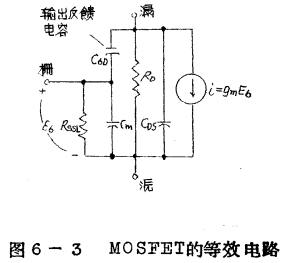

MOSFET结构的等效电路,作为研究MOSFET射频放大能力的序曲,应当描绘一下器件的等效电路,具体采用如下方法。从物理的角度来研究器件,而且希望找出器件结构与某些电学特性(这些电学特性可用分立的元件来描述。)之间的关系。图6-1为器件几何结构的示意图,图中也说明了器件有关的电学特性。如果图6-1的所有元件都考虑的话,只要根据场效应沟道电导为栅-源电压图数的事实就可以随想一个MOSFET的模型。漏

MOSFET结构的等效电路,作为研究MOSFET射频放大能力的序曲,应当描绘一下器件的等效电路,具体采用如下方法。从物理的角度来研究器件,而且希望找出器件结构与某些电学特性(这些电学特性可用分立的元件来描述。)之间的关系。图6-1为器件几何结构的示意图,图中也说明了器件有关的电学特性。如果图6-1的所有元件都考虑的话,只要根据场效应沟道电导为栅-源电压图数的事实就可以随想一个MOSFET的模型。漏

MOSFET应用的广泛性结构及电学特性,在结构和电学特性两个方面,MOS绝缘栅场效应晶体管是十分不同于通常的双极-结晶体管。它的独特性能在某些应用中是特别有用的,而在其他应用场合将受到明显的酿制。MOSFET最有用的特性之一是低频时,其输入阻抗非常高。从这个意义上来讲,通常认为MOS晶体管是真空三极管的“半导体对应物”。实际上,栅极上没有直流耦合,典型的阻抗可以高至1015欧姆的数量极。因而多级放

MOSFET应用的广泛性结构及电学特性,在结构和电学特性两个方面,MOS绝缘栅场效应晶体管是十分不同于通常的双极-结晶体管。它的独特性能在某些应用中是特别有用的,而在其他应用场合将受到明显的酿制。MOSFET最有用的特性之一是低频时,其输入阻抗非常高。从这个意义上来讲,通常认为MOS晶体管是真空三极管的“半导体对应物”。实际上,栅极上没有直流耦合,典型的阻抗可以高至1015欧姆的数量极。因而多级放

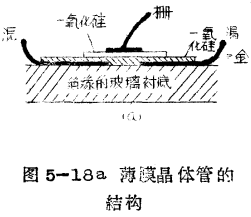

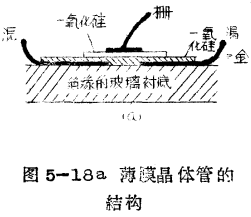

薄膜场效应晶体管,Welmer薄膜晶体管在制作工艺和材料组合方面是不同于绝缘栅MOSFET,但其结构和工作方式却是十分相似的。薄膜晶体管不用硅材料,工艺过程中也不用扩散技术。相反地,它是利用非常薄的不同材料组合而构成晶体管,各种薄层材料系生长和蒸发上去。图5-18示意了两种结构不同的薄膜晶体管。Welmer薄膜晶体管在制作工艺和材料组合方面是不同于绝缘栅MOSFET,但其结构和工作方式却是十分相似

薄膜场效应晶体管,Welmer薄膜晶体管在制作工艺和材料组合方面是不同于绝缘栅MOSFET,但其结构和工作方式却是十分相似的。薄膜晶体管不用硅材料,工艺过程中也不用扩散技术。相反地,它是利用非常薄的不同材料组合而构成晶体管,各种薄层材料系生长和蒸发上去。图5-18示意了两种结构不同的薄膜晶体管。Welmer薄膜晶体管在制作工艺和材料组合方面是不同于绝缘栅MOSFET,但其结构和工作方式却是十分相似

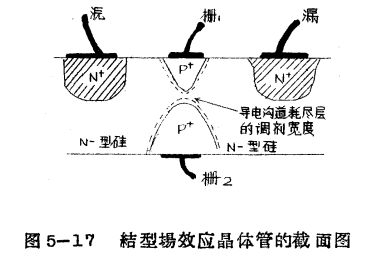

结型场效应晶体管,初期企图制作与今天所用的MOS器件相仿的面型场效应晶体管遭到了失败,因为要制备足够均匀的导体表面是不可能的。虽则外加栅压会把荷电的载流子吸引到半导体表画,但是表面陷阱可能多到把所有的电荷都俘获住,这样,电荷就变成不会移动的了。为了战胜表面态的问题,Shock1ey开拓了半导体体内的场效应与MOS相象,单极晶体管(不是单结晶体管,请别混淆-译者注)也是依靠栅压调制漏-源电极之周导电

结型场效应晶体管,初期企图制作与今天所用的MOS器件相仿的面型场效应晶体管遭到了失败,因为要制备足够均匀的导体表面是不可能的。虽则外加栅压会把荷电的载流子吸引到半导体表画,但是表面陷阱可能多到把所有的电荷都俘获住,这样,电荷就变成不会移动的了。为了战胜表面态的问题,Shock1ey开拓了半导体体内的场效应与MOS相象,单极晶体管(不是单结晶体管,请别混淆-译者注)也是依靠栅压调制漏-源电极之周导电

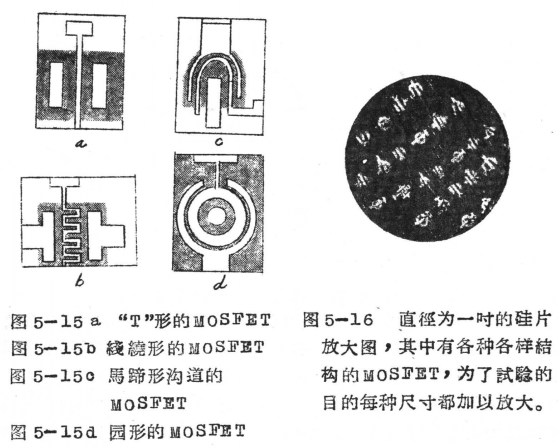

MOS晶体管的几何图形结构,绝缘栅场效应晶体管许多重要的电学特性与器件的几何结构关系极大。特别是跨导gm,VG=0时的原始漏-源电流和极间电容都是MOSFET几何结构的函数。图5-11所示的结构用以制作增强型器件。这种结构试图通过增大金属栅极和N+漏,源区之间复盖区域的间距来减小其栅-漏和栅-源电容。整个沟道仍然复以栅极,增强型器件也一定要采用这种结构。

MOS晶体管的几何图形结构,绝缘栅场效应晶体管许多重要的电学特性与器件的几何结构关系极大。特别是跨导gm,VG=0时的原始漏-源电流和极间电容都是MOSFET几何结构的函数。图5-11所示的结构用以制作增强型器件。这种结构试图通过增大金属栅极和N+漏,源区之间复盖区域的间距来减小其栅-漏和栅-源电容。整个沟道仍然复以栅极,增强型器件也一定要采用这种结构。

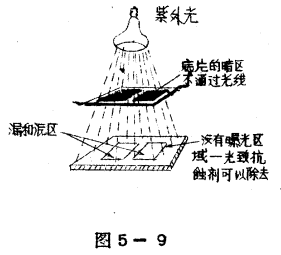

MOS管N-沟道器件的工艺,现今半导体工业中用于制作双极晶体管和双极集成电路的加工技术同样地可以用于制作MOSFET及其集成电路。实际上,MOS的制作过程,其工艺步骤较少,工艺过程较为安全而且较为简便。对于双极和MOS的制作工艺,硅片中特定区域的选操性腐腐蚀采用同样的照相技术。例如,可以来考虑一个N-沟道MOSFET的制作过程。MOS制作过程的第一步是把圆形的P-型硅棒切割成15密耳厚的硅片,硅锭

MOS管N-沟道器件的工艺,现今半导体工业中用于制作双极晶体管和双极集成电路的加工技术同样地可以用于制作MOSFET及其集成电路。实际上,MOS的制作过程,其工艺步骤较少,工艺过程较为安全而且较为简便。对于双极和MOS的制作工艺,硅片中特定区域的选操性腐腐蚀采用同样的照相技术。例如,可以来考虑一个N-沟道MOSFET的制作过程。MOS制作过程的第一步是把圆形的P-型硅棒切割成15密耳厚的硅片,硅锭

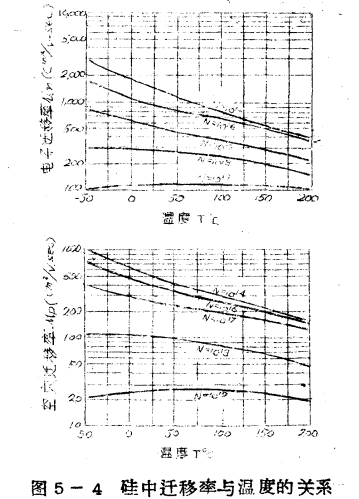

MOS管器件工作的不稳定性-温度漂移的关系,在许多方面,绝缘栅MOSFET相对于温度的稳定性要比其相应的双极晶体管好得多。实际上,这是因为MOS器件是一种多数载流子器件,而通常的p-n结晶体管却为少数载流子器件。因为少数载流子的浓度与本征浓度的平方成正比,而本征浓度又与温度(。K)的立方有很大的关系。(但是,在通常的工作条件下,多数载流子洗度与温度关系悲徽),多数载流子器件在很大的温度范围内,表现

MOS管器件工作的不稳定性-温度漂移的关系,在许多方面,绝缘栅MOSFET相对于温度的稳定性要比其相应的双极晶体管好得多。实际上,这是因为MOS器件是一种多数载流子器件,而通常的p-n结晶体管却为少数载流子器件。因为少数载流子的浓度与本征浓度的平方成正比,而本征浓度又与温度(。K)的立方有很大的关系。(但是,在通常的工作条件下,多数载流子洗度与温度关系悲徽),多数载流子器件在很大的温度范围内,表现

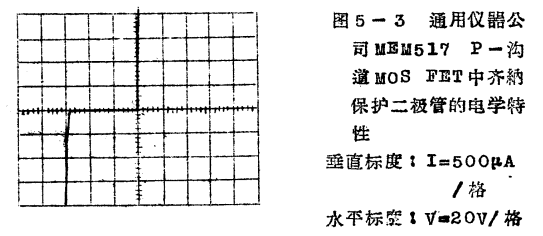

MOS晶体管中齐纳二极管保护栅极绝缘层特性示意图,典型的绝缘层约1000埃厚,它把栅极金属与硅表面隔离开来。相对于衬底而言,如果栅极上外加50伏电压,那么,绝缘层上的电场就可达到5*106伏/厘米。这么高的场强已临近于绝缘层的击穿强度。(二氧化硅的击穿强度为107伏/厘米的数量级)。栅极上出现100伏以上的任何瞬态或者阶跃电压都有可能击穿绝缘区而使栅极与衬底短路起来。实际上,由于静电荷每天都在绝

MOS晶体管中齐纳二极管保护栅极绝缘层特性示意图,典型的绝缘层约1000埃厚,它把栅极金属与硅表面隔离开来。相对于衬底而言,如果栅极上外加50伏电压,那么,绝缘层上的电场就可达到5*106伏/厘米。这么高的场强已临近于绝缘层的击穿强度。(二氧化硅的击穿强度为107伏/厘米的数量级)。栅极上出现100伏以上的任何瞬态或者阶跃电压都有可能击穿绝缘区而使栅极与衬底短路起来。实际上,由于静电荷每天都在绝

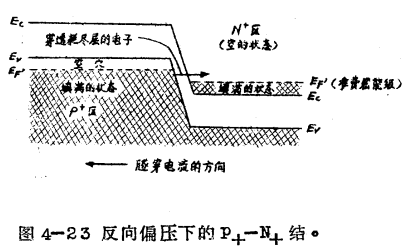

MOS管结构中的隧道-发射击穿的情况,图4-16和4-17中,随着结边界上绝缘层中电场的增大,漏-村底的击穿电压就朝原点的方向移动。不过,场强很高时,另外的过程对于击穿也开始发生作用。如果栅极部分地复盖漏区。那么,对于图4-16所示的结构,负栅压很高时,N+漏区的表面就会形成一个P+反型层。同样地,图4-17的结构加上很高的正栅压时,P+漏区的表面也会形成一个N+反型层。上述两种结果分别示于图4-

MOS管结构中的隧道-发射击穿的情况,图4-16和4-17中,随着结边界上绝缘层中电场的增大,漏-村底的击穿电压就朝原点的方向移动。不过,场强很高时,另外的过程对于击穿也开始发生作用。如果栅极部分地复盖漏区。那么,对于图4-16所示的结构,负栅压很高时,N+漏区的表面就会形成一个P+反型层。同样地,图4-17的结构加上很高的正栅压时,P+漏区的表面也会形成一个N+反型层。上述两种结果分别示于图4-

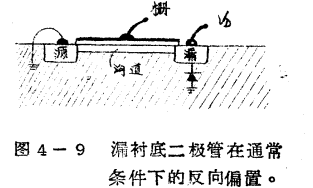

MOS管饱和之外雪崩击穿区的导电,在通常的工作条件下,MOS晶体管中的漏二极管为反向偏量。对于N-沟道的元件,这种情示于图4-9。假定恒定的电压加到栅极上,随着漏电压的增大,MOSFET就跨进恒电流的饱和区。不过,漏电压要是继续增大,器件的特性越过饱和区而进入漏电流再度增加的区域。起初增大较为缓慢,随后就变快起来。上述效应是反向偏置漏二极管开始击穿的结果。然而,正象就要看到的那样,实际的击穿早在二

MOS管饱和之外雪崩击穿区的导电,在通常的工作条件下,MOS晶体管中的漏二极管为反向偏量。对于N-沟道的元件,这种情示于图4-9。假定恒定的电压加到栅极上,随着漏电压的增大,MOSFET就跨进恒电流的饱和区。不过,漏电压要是继续增大,器件的特性越过饱和区而进入漏电流再度增加的区域。起初增大较为缓慢,随后就变快起来。上述效应是反向偏置漏二极管开始击穿的结果。然而,正象就要看到的那样,实际的击穿早在二