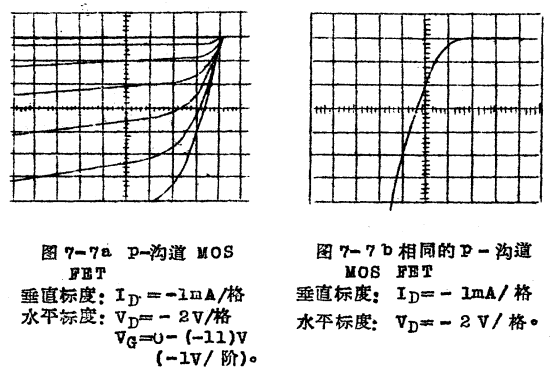

MOS数字阵列就是P-沟道逻辑电路工作原理,正象我所看到的那样,氧化了的硅表面形成N-沟道,使得制作N-沟道增强型器件变得十分困难。相邻N-沟道元件之间还会引起洩漏的问题。由于N-型表面导电机构对于空穴导电的P-沟道MOSFET是没有贡献的,因而制作P-沟道逻辑电路要此N-沟道阵列容易得多。因此,市场上出现的第一代MOS数字阵列就是P-沟道逻辑电路。实际上,MOS数字阵列是由几种基本电路组合起来而

MOS数字阵列就是P-沟道逻辑电路工作原理,正象我所看到的那样,氧化了的硅表面形成N-沟道,使得制作N-沟道增强型器件变得十分困难。相邻N-沟道元件之间还会引起洩漏的问题。由于N-型表面导电机构对于空穴导电的P-沟道MOSFET是没有贡献的,因而制作P-沟道逻辑电路要此N-沟道阵列容易得多。因此,市场上出现的第一代MOS数字阵列就是P-沟道逻辑电路。实际上,MOS数字阵列是由几种基本电路组合起来而

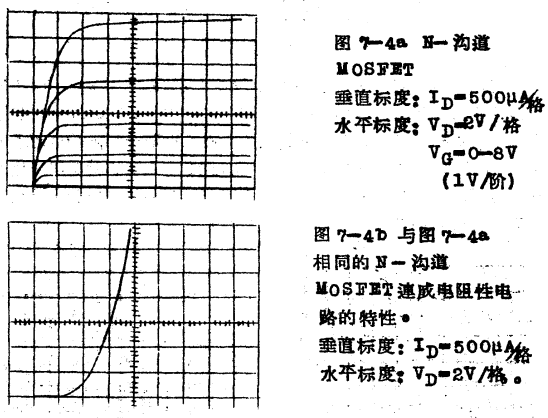

MOS晶体管共栅-漏电路及其N-P沟道电阻性组态,在MOS集成数字阵列中很少使用扩散电阻,而双极晶体管阵列通常都有扩散电阻。为了避免制造扩散电阻而增加工艺步骤,共栅-漏的MOS晶体管可以作为逻辑电路的电阻性负荷。P-沟道和N-沟道元件作为电阻性负荷的组态示于图7-1。先来考虑N-沟道的组态。对于N-沟道增强型器件而言,夹断电压(或者称阈值电压)总是正的,用VP来标记它。当VD>VG-VP时,MOS

MOS晶体管共栅-漏电路及其N-P沟道电阻性组态,在MOS集成数字阵列中很少使用扩散电阻,而双极晶体管阵列通常都有扩散电阻。为了避免制造扩散电阻而增加工艺步骤,共栅-漏的MOS晶体管可以作为逻辑电路的电阻性负荷。P-沟道和N-沟道元件作为电阻性负荷的组态示于图7-1。先来考虑N-沟道的组态。对于N-沟道增强型器件而言,夹断电压(或者称阈值电压)总是正的,用VP来标记它。当VD>VG-VP时,MOS

MOSFET逻辑电路和数字阵列,由于MOS器件具有结构简易,增强型器件开关性能良好以及尺寸小,功耗低等优点,因而,在中速数字系统中,多数电子制造厂家已把精力转到MOS阵列上。已经发展起来的小型,轻量计算机与MOS数字集成电路关系极大。集成的单块MOS阵列,好象50一位的移位寄存器,多路转换器,置位-复位触发器,非或門,非与阴以及“上-下计数器”(up-down Counters)等,其中有一些已在

MOSFET逻辑电路和数字阵列,由于MOS器件具有结构简易,增强型器件开关性能良好以及尺寸小,功耗低等优点,因而,在中速数字系统中,多数电子制造厂家已把精力转到MOS阵列上。已经发展起来的小型,轻量计算机与MOS数字集成电路关系极大。集成的单块MOS阵列,好象50一位的移位寄存器,多路转换器,置位-复位触发器,非或門,非与阴以及“上-下计数器”(up-down Counters)等,其中有一些已在

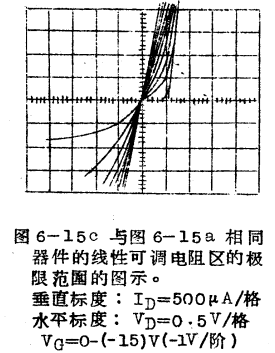

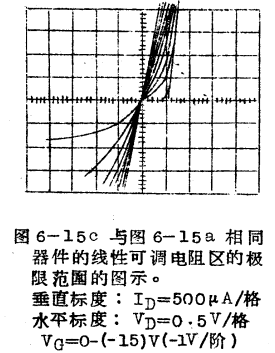

当MOS晶体管工作在漏-源电压很低的区1时,器件就起了所谓的“可调线性电阻”的作用。在区1,MOS器件,其漏源之间可当作一只电阻器,而电阻的阻值是外加栅压的函数,为了得到良好的精确度,(4·1)描述了在低漏-源电压时晶体管的工作情况。实际上,相对于源(接地)而言,如果把漏压的极性反过来,MOS晶体管仍然可以起着可调电阻的作用,这时漏压与漏-村底二极管的开通电压相近,典型值约0.5伏。对于两种极性的

当MOS晶体管工作在漏-源电压很低的区1时,器件就起了所谓的“可调线性电阻”的作用。在区1,MOS器件,其漏源之间可当作一只电阻器,而电阻的阻值是外加栅压的函数,为了得到良好的精确度,(4·1)描述了在低漏-源电压时晶体管的工作情况。实际上,相对于源(接地)而言,如果把漏压的极性反过来,MOS晶体管仍然可以起着可调电阻的作用,这时漏压与漏-村底二极管的开通电压相近,典型值约0.5伏。对于两种极性的

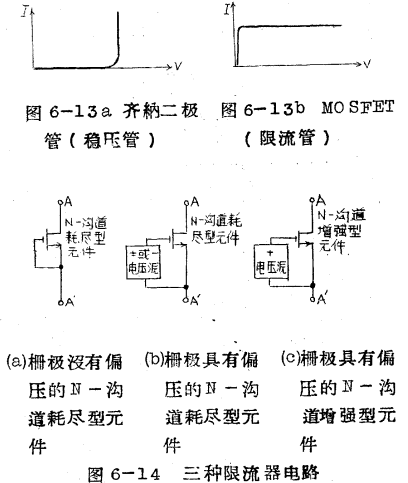

MOSFET作为限流元件-三种限流器电路图,正象齐纳的二极管可以用来限制电压低于某一个数值那样,MOS晶体管也可以用来限流。实际上,比较一下两种器件的I-V特性就可以看到,两种特性彼此相对。因为MOS工作于区1时其开态电阻不为零,所以,这对MOS器件作为一个理想的限流器是有所妨碍的,因而和齐纳二极管也不完全相应。当外加电压足以使器件工作到区2时,晶体管便能起到限流的作用。MOS晶体管作为限流的三种

MOSFET作为限流元件-三种限流器电路图,正象齐纳的二极管可以用来限制电压低于某一个数值那样,MOS晶体管也可以用来限流。实际上,比较一下两种器件的I-V特性就可以看到,两种特性彼此相对。因为MOS工作于区1时其开态电阻不为零,所以,这对MOS器件作为一个理想的限流器是有所妨碍的,因而和齐纳二极管也不完全相应。当外加电压足以使器件工作到区2时,晶体管便能起到限流的作用。MOS晶体管作为限流的三种

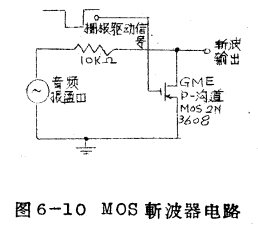

MOS斩波器电路工作原理及示意图分析,既然MOSFET是一种高效能,而特性与理想开关相近的开关器件,因而,它完全适用于斩波电路。MOS斩波器是一种固态器件,因而它不会遭到机械磨损,而现今市场上的机械斩波器,其动作的另件就不可避免地存在机械磨损,当MOS处于导通状态时,电流经过的通道没有p-n结,因而,直流偏置电压也不存在,而普通双极晶体管的斩波器就不是这样。由于MOS的绝缘栅结构,斩波器的驱动电压

MOS斩波器电路工作原理及示意图分析,既然MOSFET是一种高效能,而特性与理想开关相近的开关器件,因而,它完全适用于斩波电路。MOS斩波器是一种固态器件,因而它不会遭到机械磨损,而现今市场上的机械斩波器,其动作的另件就不可避免地存在机械磨损,当MOS处于导通状态时,电流经过的通道没有p-n结,因而,直流偏置电压也不存在,而普通双极晶体管的斩波器就不是这样。由于MOS的绝缘栅结构,斩波器的驱动电压

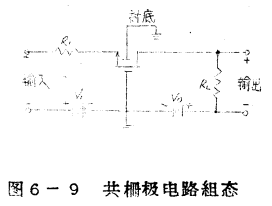

MOS共栅极工作电路,图6-9所示的共栅极组态是一种独特的电路,其中MOSFET不受栅压的控制。更确恰地说,源作为控制端。共栅极电路组态把低输入阻抗转换为高输出阻抗,虽然它的增益通常要比1大,但是它总比MOS放大器的增益过底小,图6-9电路中的MOSFET为N-沟道耗尽型元件,其直流工作点由电压V1来控制。

MOS共栅极工作电路,图6-9所示的共栅极组态是一种独特的电路,其中MOSFET不受栅压的控制。更确恰地说,源作为控制端。共栅极电路组态把低输入阻抗转换为高输出阻抗,虽然它的增益通常要比1大,但是它总比MOS放大器的增益过底小,图6-9电路中的MOSFET为N-沟道耗尽型元件,其直流工作点由电压V1来控制。

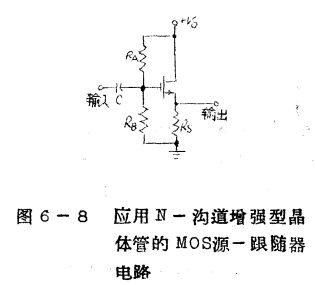

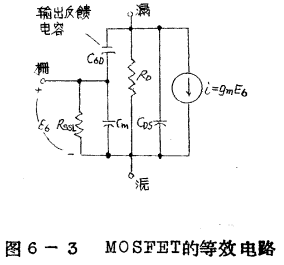

MOS源跟随器电路,MOS源跟随器电路可以达到输入阻抗高而输出阻抗低的目的,这时增益稍小于1,同时讯号相位没倒相。源跟随器的电路结构示于图6-8。和MOS放大器一样,偏置电阻RA和RB的阻值足够高,因而增益的表示式不包含RA和RB,隔直电容C的情况也是这样。应用图6-3MOS的等效电路,我们就可以按照6.3.1所用的程序来推导MOS源跟随器的增益。推导过程,完全依照前面的思路。源跟随器低频增益的结

MOS源跟随器电路,MOS源跟随器电路可以达到输入阻抗高而输出阻抗低的目的,这时增益稍小于1,同时讯号相位没倒相。源跟随器的电路结构示于图6-8。和MOS放大器一样,偏置电阻RA和RB的阻值足够高,因而增益的表示式不包含RA和RB,隔直电容C的情况也是这样。应用图6-3MOS的等效电路,我们就可以按照6.3.1所用的程序来推导MOS源跟随器的增益。推导过程,完全依照前面的思路。源跟随器低频增益的结

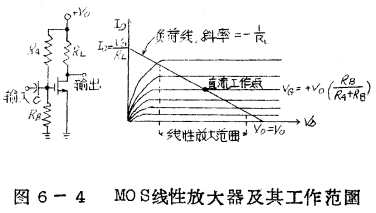

MOS放大器的增益当电路被偏置在线性放大区域时,图6-3的等效电路可以用来描述图6-4放大器中使用的N-沟道增强型MOSFET的工作。如果我们用电压源VS(VS的内阻为R1)来驱动放大器,就得到如下的电路(V1=EG):应用Norton理论并代人一个等效的输入电流源,我们就得到用导纳表示的电路。根据图6-7定义,导纳为:把克希荷夫电流定律应用到节点A和B,我就得到上述式子用可矩障的型式重写为:如果

MOS放大器的增益当电路被偏置在线性放大区域时,图6-3的等效电路可以用来描述图6-4放大器中使用的N-沟道增强型MOSFET的工作。如果我们用电压源VS(VS的内阻为R1)来驱动放大器,就得到如下的电路(V1=EG):应用Norton理论并代人一个等效的输入电流源,我们就得到用导纳表示的电路。根据图6-7定义,导纳为:把克希荷夫电流定律应用到节点A和B,我就得到上述式子用可矩障的型式重写为:如果

MOSFET作射频放大器,考虑图6-4线性放大器电路,其中应用N-沟道增强型的晶体管。线性放大的动态范围直流工作点是由负荷电阻,偏置电源电压,电阻RA和RB(决定其直流的工作栅压)以及MOSEFT本身的特性性来决定的。MOSFET作射频放大器。当MOSFET被偏置到线性放,就可应用图6-3的等效电路。下一节还要应用等效电路来推导放大器增益的表示式。考虑图6-4线性放大器电路,其中应用N-沟道增强型

MOSFET作射频放大器,考虑图6-4线性放大器电路,其中应用N-沟道增强型的晶体管。线性放大的动态范围直流工作点是由负荷电阻,偏置电源电压,电阻RA和RB(决定其直流的工作栅压)以及MOSEFT本身的特性性来决定的。MOSFET作射频放大器。当MOSFET被偏置到线性放,就可应用图6-3的等效电路。下一节还要应用等效电路来推导放大器增益的表示式。考虑图6-4线性放大器电路,其中应用N-沟道增强型