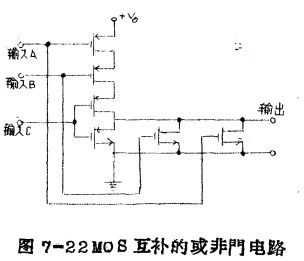

互补的MOS“或非門”,实现“或非”功能所用的互补电路示于图7~22。图示电路为一个三端输入的“或非門”。这时,P-沟道元件是串联连接的,而N-沟道元件是并联的。和“与非門”的情况一样,两种输入讯号随意组合时,从偏置电源到地的电流通路。至少会被一只关态的晶体管阻塞。除了三个输入都是0伏之外,至少有一只P-沟道元件被关断,而与之相应的一只N-沟道元件导通,因而输出为0伏。只有在所有的输入为0伏时,输

互补的MOS“或非門”,实现“或非”功能所用的互补电路示于图7~22。图示电路为一个三端输入的“或非門”。这时,P-沟道元件是串联连接的,而N-沟道元件是并联的。和“与非門”的情况一样,两种输入讯号随意组合时,从偏置电源到地的电流通路。至少会被一只关态的晶体管阻塞。除了三个输入都是0伏之外,至少有一只P-沟道元件被关断,而与之相应的一只N-沟道元件导通,因而输出为0伏。只有在所有的输入为0伏时,输

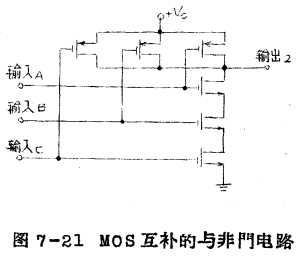

互补MOS与非門,用图7-21所示的互补电路就可以实现“与非”的逻辑功能(但其功耗最小)。现在考虑一个三端输入的“与非”門。P-沟道元件为并联连接,而N-沟道元件都为串联连接。用+Vo和0伏电压作为讯号电平,无论这两种讯号在输入端为何组合,当栅极不是处于转换信号的时刻,至少有一只关态晶体管会阻塞偏压电源到地的电流通路。除了所有输入均为人+Vo之外,至少有一只N-沟道晶体管关断,和一只P-沟道晶体管

互补MOS与非門,用图7-21所示的互补电路就可以实现“与非”的逻辑功能(但其功耗最小)。现在考虑一个三端输入的“与非”門。P-沟道元件为并联连接,而N-沟道元件都为串联连接。用+Vo和0伏电压作为讯号电平,无论这两种讯号在输入端为何组合,当栅极不是处于转换信号的时刻,至少有一只关态晶体管会阻塞偏压电源到地的电流通路。除了所有输入均为人+Vo之外,至少有一只N-沟道晶体管关断,和一只P-沟道晶体管

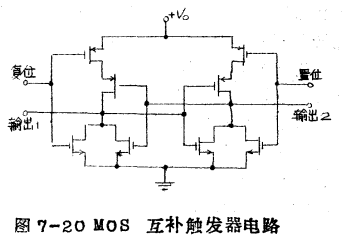

从P-沟道倒相器转变到互补的倒相器,其中共栅-漏P-沟道负荷被N-沟道元件所取代。(而N-沟道元件与下面的P-沟道元件的栅极是连在一道的)把§7.5P-沟道MOS触发器作相仿的修改就设计出互补的触发器,它可实现P-沟道触发器的功能,但其稳态功耗可以忽略不计。互补触发器的电路示于图7-20。

从P-沟道倒相器转变到互补的倒相器,其中共栅-漏P-沟道负荷被N-沟道元件所取代。(而N-沟道元件与下面的P-沟道元件的栅极是连在一道的)把§7.5P-沟道MOS触发器作相仿的修改就设计出互补的触发器,它可实现P-沟道触发器的功能,但其稳态功耗可以忽略不计。互补触发器的电路示于图7-20。

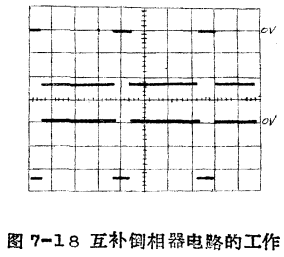

所述的P-沟道逻辑的倒相器,当输入端加上负讯号时要洩放相当数量的电流。在洩放电流时就有功率耗散。MOS互补倒相器可以实现与P-沟道倒相器完全相同的功能,不过,两种输入状态,都不洩放可观量的电流。因而除其开关的时间之外,互补倒相器的功耗是微乎其微的。互补倒相电路示于图7-17注意到每只晶体管的源都与各自的衬底连在一道,与倒相器关连的逻辑讯号为0伏和-Vo伏。0伏输入讯号将使P-沟道晶体管关断,而N-

所述的P-沟道逻辑的倒相器,当输入端加上负讯号时要洩放相当数量的电流。在洩放电流时就有功率耗散。MOS互补倒相器可以实现与P-沟道倒相器完全相同的功能,不过,两种输入状态,都不洩放可观量的电流。因而除其开关的时间之外,互补倒相器的功耗是微乎其微的。互补倒相电路示于图7-17注意到每只晶体管的源都与各自的衬底连在一道,与倒相器关连的逻辑讯号为0伏和-Vo伏。0伏输入讯号将使P-沟道晶体管关断,而N-

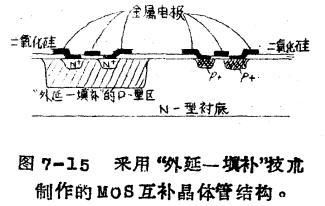

金属-绝缘层-半导体场效应晶体管最有前途的应用可能就是N-和P-沟道器件制作在同一个衬底上的低功耗数字系统。由于稳态功耗常低,结构相当简单以及MOSFET里尺寸小等优点,因而可以期望,这些数字系统每单位面积的“包封密度”要比相当的双极晶体管阵列大。使用N-和P-沟道器件互补逻辑的有关优点已被公认很长一段时间了,但是在同一衬底上制作两种类型器件的工艺问题直到最近才得到解决。毫无疑问,制作互补MOSF

金属-绝缘层-半导体场效应晶体管最有前途的应用可能就是N-和P-沟道器件制作在同一个衬底上的低功耗数字系统。由于稳态功耗常低,结构相当简单以及MOSFET里尺寸小等优点,因而可以期望,这些数字系统每单位面积的“包封密度”要比相当的双极晶体管阵列大。使用N-和P-沟道器件互补逻辑的有关优点已被公认很长一段时间了,但是在同一衬底上制作两种类型器件的工艺问题直到最近才得到解决。毫无疑问,制作互补MOSF

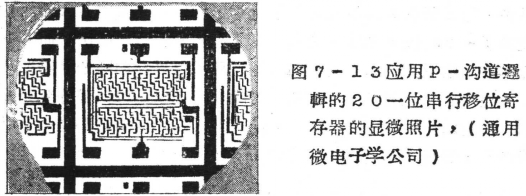

解析复杂的集成MOS阵列基础原理分析应用前节所述的P-沟道MOS倒相器、触发器、与門,或門、或非門以及与非門,就可以制作非常复杂的MOS数字阵列。图7-13是复杂数字阵列的示例,它是“飞歌-福特公司通用微电子学部”制作的20-位串行移位寄存器,其中使用120个集成的MOSFET标准逻辑元件,采用新的技术使之与制作复杂的P-沟道阵列的工艺结合起来,相当复杂的互补MOS阵列也开始发展起来。这些所谓的“

解析复杂的集成MOS阵列基础原理分析应用前节所述的P-沟道MOS倒相器、触发器、与門,或門、或非門以及与非門,就可以制作非常复杂的MOS数字阵列。图7-13是复杂数字阵列的示例,它是“飞歌-福特公司通用微电子学部”制作的20-位串行移位寄存器,其中使用120个集成的MOSFET标准逻辑元件,采用新的技术使之与制作复杂的P-沟道阵列的工艺结合起来,相当复杂的互补MOS阵列也开始发展起来。这些所谓的“

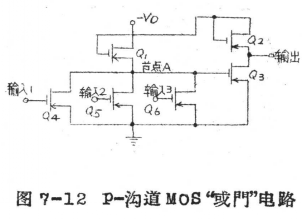

在二进位制中,“或門”执行着加法的逻辑功能。只要任何一个输入为“1”,門的输出就是“1”。只有所有的输入都为“0”,門的翰出才是“0”。MOS或門的P-沟道电路组态示于图7-12 Q1,Q4,Q5和Q6所组成的“或門”,是辅助部分,而晶体管Q2和Q3用组成一个倒相器。Q1和Q2是电阻性负荷。如果三个输入中任何一个输入端等于-Vo伏,与此输入相应的晶体管就导通,电流就流经这只管子,因而A点电位几乎等

在二进位制中,“或門”执行着加法的逻辑功能。只要任何一个输入为“1”,門的输出就是“1”。只有所有的输入都为“0”,門的翰出才是“0”。MOS或門的P-沟道电路组态示于图7-12 Q1,Q4,Q5和Q6所组成的“或門”,是辅助部分,而晶体管Q2和Q3用组成一个倒相器。Q1和Q2是电阻性负荷。如果三个输入中任何一个输入端等于-Vo伏,与此输入相应的晶体管就导通,电流就流经这只管子,因而A点电位几乎等

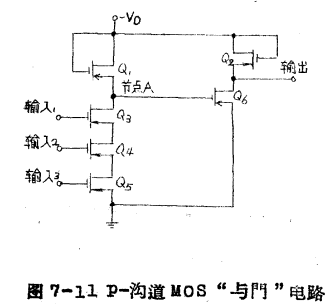

在二进位制中,与门实现其乘法的逻辑功能。一个MOS管P沟道的“与門”示于图7-11。如果采用“1”和“0”逻辑电平,那么,与門的所有输入必须都是“1”,输出才可以得到“1”。如果有一个以上的输入为“0”,则門的输出也是“0”。Q1和Q2系接成共栅-漏组态,它是作为开关过程的负荷。如果任何输入为“0”时,A点的电压就近似地等于-Vo,因为与“0”输入相应的晶体管处于关断状态。节点A的负电压使Q6导通

在二进位制中,与门实现其乘法的逻辑功能。一个MOS管P沟道的“与門”示于图7-11。如果采用“1”和“0”逻辑电平,那么,与門的所有输入必须都是“1”,输出才可以得到“1”。如果有一个以上的输入为“0”,则門的输出也是“0”。Q1和Q2系接成共栅-漏组态,它是作为开关过程的负荷。如果任何输入为“0”时,A点的电压就近似地等于-Vo,因为与“0”输入相应的晶体管处于关断状态。节点A的负电压使Q6导通

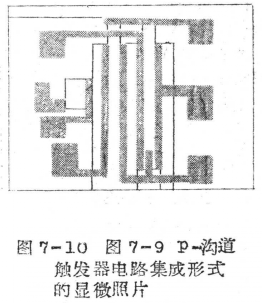

P-沟道MOS触发器MOS管P-沟道触发器的一种电路示于图7-9。触发器也叫做“双稳多谐振荡器”。当输出1为两个逻辑电平之一时,翰出就位于另一个逻辑电平,反之亦然。每种状态都是稳定的。晶体管Q1和Q2都接成共栅-漏组态,它们在触发器的两边各起一个负荷电阻的作用。和倒相器情况一样,负荷晶体管的跨导应为有源晶体管Q3,Q4,Q5和Q6跨导的十分之一左右。输入逻辑讯号还是-Vo和V伏。如果-Vo伏的负脈

P-沟道MOS触发器MOS管P-沟道触发器的一种电路示于图7-9。触发器也叫做“双稳多谐振荡器”。当输出1为两个逻辑电平之一时,翰出就位于另一个逻辑电平,反之亦然。每种状态都是稳定的。晶体管Q1和Q2都接成共栅-漏组态,它们在触发器的两边各起一个负荷电阻的作用。和倒相器情况一样,负荷晶体管的跨导应为有源晶体管Q3,Q4,Q5和Q6跨导的十分之一左右。输入逻辑讯号还是-Vo和V伏。如果-Vo伏的负脈

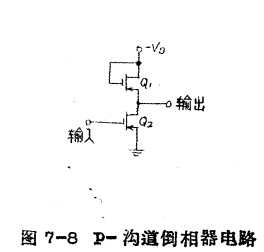

P-沟道倒相器图7-8所示的倒相器电路可能是最简单的P-沟道数字“标准准逻辑元件”。如果使用的逻辑电平为-VO伏和0伏,输入端加上任何一个电平电压时,输出端就得到另一个电平电压。晶体管Q1连接成§7.2所述的共栅-漏组态,它是作为负荷电阻用的。为了简化对电路的定性描写,我们假定所有晶体管的阈值电压都是零,那么,输入端加上-VO电压将使晶体管Q2导通,从而使电源电压大部分都降落在晶体管Q1上。因此,

P-沟道倒相器图7-8所示的倒相器电路可能是最简单的P-沟道数字“标准准逻辑元件”。如果使用的逻辑电平为-VO伏和0伏,输入端加上任何一个电平电压时,输出端就得到另一个电平电压。晶体管Q1连接成§7.2所述的共栅-漏组态,它是作为负荷电阻用的。为了简化对电路的定性描写,我们假定所有晶体管的阈值电压都是零,那么,输入端加上-VO电压将使晶体管Q2导通,从而使电源电压大部分都降落在晶体管Q1上。因此,