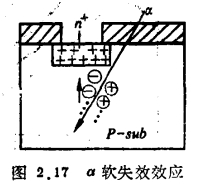

VLSI尺寸缩小的限制分析特性及其改善主要原因Scaling-down虽能极大改善VLSI性能,但当尺寸缩得太小,会对器件性能有不利影响。广义来说,Scaling-down的限制分为两类情况。一类是灾难性的,即影响器件的功能及可靠性,其中最突出的是热载流子效应。当沟道电场和栅电场增强时,热载流子向栅氧化的注入引起器件不稳定,已成为短沟( 1.5μm)VLSI中的严重问题。目前普遍采用的LDD结构虽

VLSI尺寸缩小的限制分析特性及其改善主要原因Scaling-down虽能极大改善VLSI性能,但当尺寸缩得太小,会对器件性能有不利影响。广义来说,Scaling-down的限制分为两类情况。一类是灾难性的,即影响器件的功能及可靠性,其中最突出的是热载流子效应。当沟道电场和栅电场增强时,热载流子向栅氧化的注入引起器件不稳定,已成为短沟( 1.5μm)VLSI中的严重问题。目前普遍采用的LDD结构虽

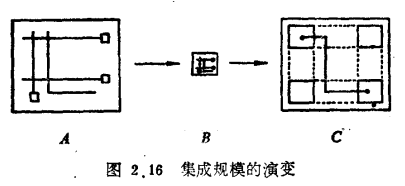

MOS器件VLSI中内连线对延迟时间的影响的分析随着单个器件尺寸日益缩小,性能改善,总的集成规模越来越大,VLSI的内连线对电路的时间延迟起着决定性的作用,已成为限制VLSI高速化的主要因素。内连线的影响通过延迟RC反映出来。其中R、C分别为连线的杂散分布电阻和电容。连线电阻与线的尺寸及所用的材料有关,而与所用材料的关系更为密切。在VLSI工艺中可以采用多种材料作为连线,其电阻率越低越好。铝线的电

MOS器件VLSI中内连线对延迟时间的影响的分析随着单个器件尺寸日益缩小,性能改善,总的集成规模越来越大,VLSI的内连线对电路的时间延迟起着决定性的作用,已成为限制VLSI高速化的主要因素。内连线的影响通过延迟RC反映出来。其中R、C分别为连线的杂散分布电阻和电容。连线电阻与线的尺寸及所用的材料有关,而与所用材料的关系更为密切。在VLSI工艺中可以采用多种材料作为连线,其电阻率越低越好。铝线的电

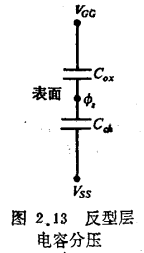

MOS反型层电容分压特性及其公式分析在前面的公式推导中,当VGVT时,忽略了反型层表面势Φ。随VG的变化,假设强反型的表面势Φs=2▏ΦP▕是恒定值,但这种假设显然是一种近似。因为一般沟道电容Cch比Cox大得多,在这种情况下,如图2.13所示,G极电位VG的变化并不引起表面电势Φs的变化,近似是合理的。但当tox大大缩小时,则Cox与Cch可以比拟,结果Φs随VG增加而增加,跨导会比不考虑Φs变

MOS反型层电容分压特性及其公式分析在前面的公式推导中,当VGVT时,忽略了反型层表面势Φ。随VG的变化,假设强反型的表面势Φs=2▏ΦP▕是恒定值,但这种假设显然是一种近似。因为一般沟道电容Cch比Cox大得多,在这种情况下,如图2.13所示,G极电位VG的变化并不引起表面电势Φs的变化,近似是合理的。但当tox大大缩小时,则Cox与Cch可以比拟,结果Φs随VG增加而增加,跨导会比不考虑Φs变

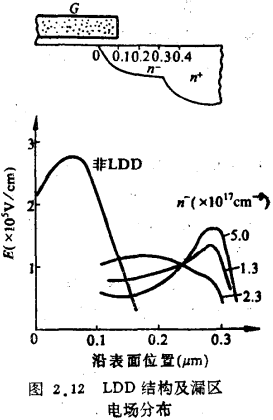

解析热载流子效应的轻掺杂漏区结构(LDD)为了减弱热电子效应,提出了多种器件结构的改进方案。目前比较成功的通用方法是采用轻掺杂漏区结构,简称LDD。其结构是在D区靠沟道一侧做一个很短(约0.2~0.3μm)的n-区,作为漏电场的缓冲区。这样的结构会使漏区的Em大大下降。图2.12是LDD的结构图及n-为各种值时计算出的漏区电扬分布,并与无n-区的普通结构进行比较。由图可见,无n-的普通结构的最大电

解析热载流子效应的轻掺杂漏区结构(LDD)为了减弱热电子效应,提出了多种器件结构的改进方案。目前比较成功的通用方法是采用轻掺杂漏区结构,简称LDD。其结构是在D区靠沟道一侧做一个很短(约0.2~0.3μm)的n-区,作为漏电场的缓冲区。这样的结构会使漏区的Em大大下降。图2.12是LDD的结构图及n-为各种值时计算出的漏区电扬分布,并与无n-区的普通结构进行比较。由图可见,无n-的普通结构的最大电

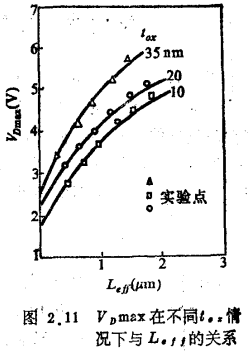

器件尺寸和电压的限制为了保证Em Eo,沟道长度L必定有下限,电源电压必定有上限。由(2.8)式可得:其中K=√3t0=x。(2.9)式中的Vosa,代入上式,并考虑在最坏情况,Vo=vn使Io达到lomax,由此可得:V0 21KE.+V,+I(KE.-V)2+4E。L(KE'-Vr)]1/}(2.13)图2.11为用上式计算不同tox下的Vomax与L。的关系以及按l0*10151。的

器件尺寸和电压的限制为了保证Em Eo,沟道长度L必定有下限,电源电压必定有上限。由(2.8)式可得:其中K=√3t0=x。(2.9)式中的Vosa,代入上式,并考虑在最坏情况,Vo=vn使Io达到lomax,由此可得:V0 21KE.+V,+I(KE.-V)2+4E。L(KE'-Vr)]1/}(2.13)图2.11为用上式计算不同tox下的Vomax与L。的关系以及按l0*10151。的

分析热载流子效应的临界电场Eo与定性基础类似pn结有一个临界击穿电场,热电子效应也可以定义一个临界电场E′o,这个电场决定于器件长期稳定性所容许的程度。有人定义Em=E′o=1.5×105V/cm为临界电场。这时有:在上述的热电子流数值下,器件能够工作几十年而栅电荷并不引起明显的变化。当然,这样定义的E′o有不少人为性,而且为了保险而显得苛刻。联系方式:邹先生联系电话:0755-83888366-

分析热载流子效应的临界电场Eo与定性基础类似pn结有一个临界击穿电场,热电子效应也可以定义一个临界电场E′o,这个电场决定于器件长期稳定性所容许的程度。有人定义Em=E′o=1.5×105V/cm为临界电场。这时有:在上述的热电子流数值下,器件能够工作几十年而栅电荷并不引起明显的变化。当然,这样定义的E′o有不少人为性,而且为了保险而显得苛刻。联系方式:邹先生联系电话:0755-83888366-

热载流子效应沟道场的简化模型与特性分析要计算热电子流,必须求解二维或三维泊松方程,求出沟道中电场分布,特别是在漏端附近的最大电场Em。为了精确求解,应采用数值解的方法,但实际应用中不太方便,物理意义不直观。为此,可采用解析式近似:其中是短沟管的速度饱和电压。由第一章的(1.57)式知其中Ec为饱和电场,约为。由式(2.8)及(2.9)看出,在相同的VD条件下热电子效应与t密切相关。越小,则Em越大

热载流子效应沟道场的简化模型与特性分析要计算热电子流,必须求解二维或三维泊松方程,求出沟道中电场分布,特别是在漏端附近的最大电场Em。为了精确求解,应采用数值解的方法,但实际应用中不太方便,物理意义不直观。为此,可采用解析式近似:其中是短沟管的速度饱和电压。由第一章的(1.57)式知其中Ec为饱和电场,约为。由式(2.8)及(2.9)看出,在相同的VD条件下热电子效应与t密切相关。越小,则Em越大

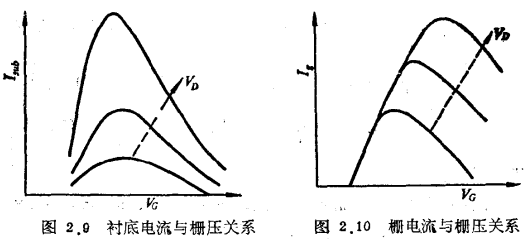

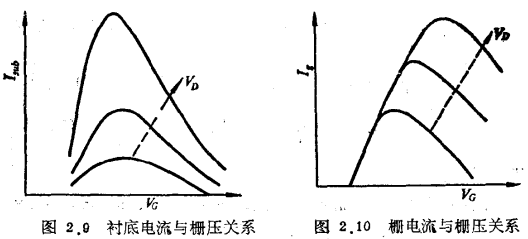

热载流子效应由于沟道越来越短,栅氧化层越来越薄,而电源电压又要保持5V标准,结果使沟道内的横向和纵向电场大大加强。横向强电场使导电载流子加速,并获得高能量,这些高能量的载流子即为热载流子。它们在强纵向栅场作用下越过Si/SiO2,势垒进入SiO2中,使栅氧化层中的电荷发生变化,造成开启电压的漂移,引起器件特性不稳定。同时,部分高能载流子与晶格碰撞,产生电子空穴对,如图2.8所示。空穴为衬底所收集,

热载流子效应由于沟道越来越短,栅氧化层越来越薄,而电源电压又要保持5V标准,结果使沟道内的横向和纵向电场大大加强。横向强电场使导电载流子加速,并获得高能量,这些高能量的载流子即为热载流子。它们在强纵向栅场作用下越过Si/SiO2,势垒进入SiO2中,使栅氧化层中的电荷发生变化,造成开启电压的漂移,引起器件特性不稳定。同时,部分高能载流子与晶格碰撞,产生电子空穴对,如图2.8所示。空穴为衬底所收集,

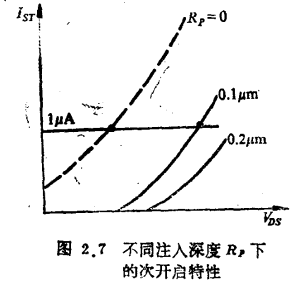

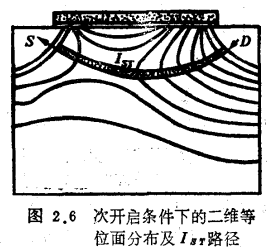

MOS管器件穿通机理的工艺结构改造措施由于表面栅场的抑制作用,VDS足够大时,S/D之间的电流不是从表面流过,而按电力线方向从次表面流过,如图2.6中的箭头所示。在这种情况下VG对次开启电流的影响就大大减弱,这就是曲线在B点汇聚的原因。由上述的分析可知,在相同的Leff条件下,次表面的掺杂浓度对穿通电压起着十分重要的作用。因此,提高穿通电压的主要措施是在栅下次表面区进行一次增加杂质浓度的抗穿通注入

MOS管器件穿通机理的工艺结构改造措施由于表面栅场的抑制作用,VDS足够大时,S/D之间的电流不是从表面流过,而按电力线方向从次表面流过,如图2.6中的箭头所示。在这种情况下VG对次开启电流的影响就大大减弱,这就是曲线在B点汇聚的原因。由上述的分析可知,在相同的Leff条件下,次表面的掺杂浓度对穿通电压起着十分重要的作用。因此,提高穿通电压的主要措施是在栅下次表面区进行一次增加杂质浓度的抗穿通注入

详解MOS管器件的穿通特性及其工艺结构尺寸缩小,沟道缩短,首先碰到的问题是S/D穿通。实验发现,当VG VT时,VDS达到一定值(即穿通电压VPT)后,IDS急剧增加,这种现象就是穿通。图2.1为MOS器件的穿通特性。有效沟道长度越短,穿通电压VPT越低。经验的结果为:因此,当Leff足够小时,如设计不当,VPT会小于VDD。这样,短沟器件无法正常工作。为了保证在较短的Leff条件下能保持足够VP

详解MOS管器件的穿通特性及其工艺结构尺寸缩小,沟道缩短,首先碰到的问题是S/D穿通。实验发现,当VG VT时,VDS达到一定值(即穿通电压VPT)后,IDS急剧增加,这种现象就是穿通。图2.1为MOS器件的穿通特性。有效沟道长度越短,穿通电压VPT越低。经验的结果为:因此,当Leff足够小时,如设计不当,VPT会小于VDD。这样,短沟器件无法正常工作。为了保证在较短的Leff条件下能保持足够VP