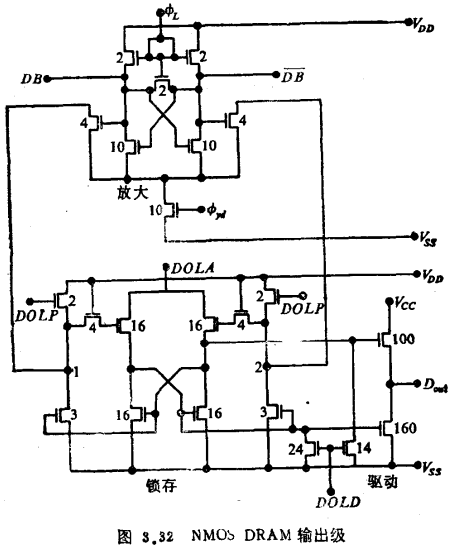

NMOS DRAM输出级电路图分析及其基础作用DRAM的输出级一般由输出放大器、输出锁存器和输出缓冲器三部分所组成。图3.32为一种典型电路。放大器与S/R基本类似,但管子W/L要大一些,以增加它的驱动能力。输出锁存器与地址输入缓冲器的第一级类似,DOLP时钟为结点1、2的高电平预充时钟。根据放大器的两端输出置1、2结点为一高一低电平,然后传入由触发器形式组成的数据锁存器,该数据将锁存至下一个周期

NMOS DRAM输出级电路图分析及其基础作用DRAM的输出级一般由输出放大器、输出锁存器和输出缓冲器三部分所组成。图3.32为一种典型电路。放大器与S/R基本类似,但管子W/L要大一些,以增加它的驱动能力。输出锁存器与地址输入缓冲器的第一级类似,DOLP时钟为结点1、2的高电平预充时钟。根据放大器的两端输出置1、2结点为一高一低电平,然后传入由触发器形式组成的数据锁存器,该数据将锁存至下一个周期

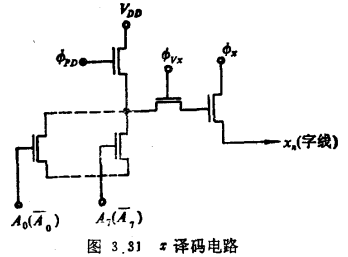

分析NMOS DRAM译码电路的主要作用由前述可知,在DRAM中地址译码采用分时形式。图3.31是x译码电路,其中фPD为译码器的预充时钟。电路采用NOR门形式,由Ao(Ao)至A7()8个来自地址缓冲器的地址码NOR。фvx是译码输出的锁存时钟。фx是驱动字线的时钟,它对选上的字线有自举作用。因此使选上字线得到好的高电平。同时,也增强对该字线的驱动能力,缩短字线的延迟。这对提高电路的速度起着重要

分析NMOS DRAM译码电路的主要作用由前述可知,在DRAM中地址译码采用分时形式。图3.31是x译码电路,其中фPD为译码器的预充时钟。电路采用NOR门形式,由Ao(Ao)至A7()8个来自地址缓冲器的地址码NOR。фvx是译码输出的锁存时钟。фx是驱动字线的时钟,它对选上的字线有自举作用。因此使选上字线得到好的高电平。同时,也增强对该字线的驱动能力,缩短字线的延迟。这对提高电路的速度起着重要

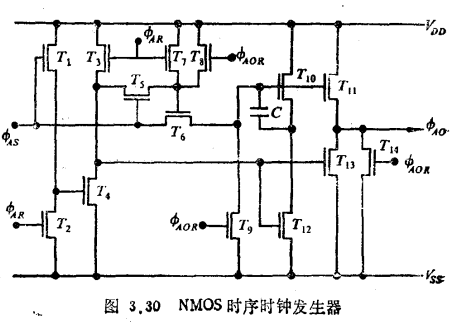

NMOS DRAM时序时钟发生器功能及电路图分析在DRAM中有众多的时钟,它们是由外主时钟和(读写控制)触发形成的。由上述输入缓冲器的例子可以看出,它们要按一定时序配合各部分电路工作,组成时钟链。为了更具体说明问题,我们将以фAO发生器为典型实例进行分析。图3.30就是它的电路图。一个时钟发生器除了要求时序配合外,还要求输出高电平达到电源电平VDD以及大的驱动能力。фAO由фAS驱动,фAS通过T

NMOS DRAM时序时钟发生器功能及电路图分析在DRAM中有众多的时钟,它们是由外主时钟和(读写控制)触发形成的。由上述输入缓冲器的例子可以看出,它们要按一定时序配合各部分电路工作,组成时钟链。为了更具体说明问题,我们将以фAO发生器为典型实例进行分析。图3.30就是它的电路图。一个时钟发生器除了要求时序配合外,还要求输出高电平达到电源电平VDD以及大的驱动能力。фAO由фAS驱动,фAS通过T

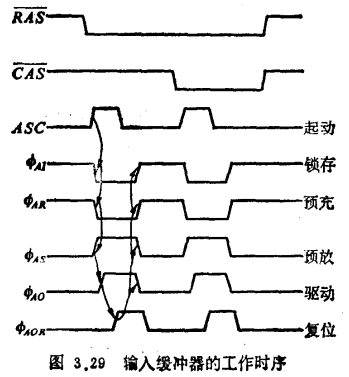

NMOS地址输入缓冲器性能及其工作程序图示解析图3.28为其电路图。它包含有4相时钟,进行全动态工作,其核心是由T1、T2、T3、T4所组成的不对称触发器,由于T1的β大于T2,因此当输入是低电平时,在фAS时钟加上后,触发器处于自然稳定状态,为低电平,为高电平,再经两级动态电路驱动,由及输出到译码器电路。当输入是高电平时,被强迫置低电平,和分别为低电平和高电平,输到译码器电路。整个电路的4相时钟

NMOS地址输入缓冲器性能及其工作程序图示解析图3.28为其电路图。它包含有4相时钟,进行全动态工作,其核心是由T1、T2、T3、T4所组成的不对称触发器,由于T1的β大于T2,因此当输入是低电平时,在фAS时钟加上后,触发器处于自然稳定状态,为低电平,为高电平,再经两级动态电路驱动,由及输出到译码器电路。当输入是高电平时,被强迫置低电平,和分别为低电平和高电平,输到译码器电路。整个电路的4相时钟

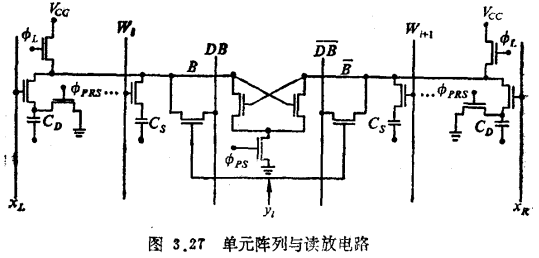

NMOS DRAM单元阵列及读放电路图分析本节将较全面地介绍各个子电路的形式。为了具体化,我们将以某种典型的NMOSDRAM为例。一、单元阵列及读放图3.27中包括单元、虚单元和S/R,是阵列中的一个小局部。采用半电荷虚单元,фPRS是使CD上存储电荷置“0”的脉冲。输出为两对数据母线,与上节介绍的情况相同。左右各设一条虚单元字线XL,及XR。фL为位线预充时钟。联系方式:邹先生联系电话:0755

NMOS DRAM单元阵列及读放电路图分析本节将较全面地介绍各个子电路的形式。为了具体化,我们将以某种典型的NMOSDRAM为例。一、单元阵列及读放图3.27中包括单元、虚单元和S/R,是阵列中的一个小局部。采用半电荷虚单元,фPRS是使CD上存储电荷置“0”的脉冲。输出为两对数据母线,与上节介绍的情况相同。左右各设一条虚单元字线XL,及XR。фL为位线预充时钟。联系方式:邹先生联系电话:0755

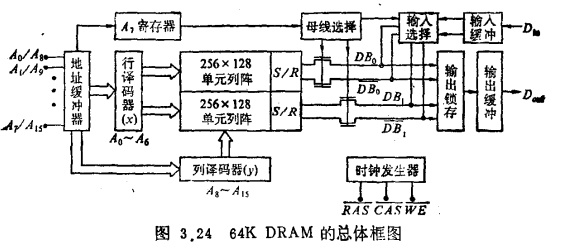

64K NMOS DRAM总体框图结构及单元阵列布局我们以一种64K NMOS DRAM为例。它是80年代初期的产品,总体框图如图3.24所示。单元列阵为256×256。为了减少x译码器的数量,将列阵分成两半,各为256×128。行地址只有7个送行译码器,因此共有128个行译码器。每个译码讯号驱动两条字线,分配在上下子列阵中各一条。列地址8个均送256个y译码器,进行列选。由此列阵输出两对讯号,上

64K NMOS DRAM总体框图结构及单元阵列布局我们以一种64K NMOS DRAM为例。它是80年代初期的产品,总体框图如图3.24所示。单元列阵为256×256。为了减少x译码器的数量,将列阵分成两半,各为256×128。行地址只有7个送行译码器,因此共有128个行译码器。每个译码讯号驱动两条字线,分配在上下子列阵中各一条。列地址8个均送256个y译码器,进行列选。由此列阵输出两对讯号,上

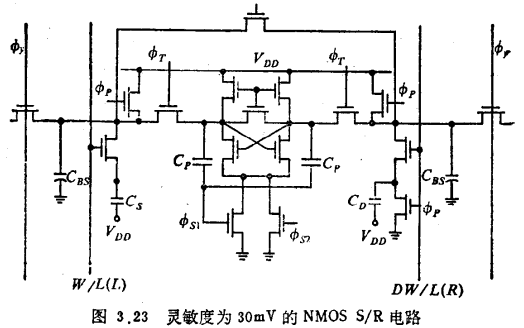

S/R电路设计和性能及主要重点技术措施分析设计性能好的S/R要求综合考虑如下四点。(1)高灵敏度S/R灵敏度越高,允许单元的存储电容越小,集成容量越大。(2)低功耗由于VLSI DRAM中S/R众多,因此它们的功耗直接影响DRAM的总功耗。为此采用全动态检测,以避免直流通路引起的可观功耗。(3)高终态“1”电平全动态检测不可避免会有高电平的损失。但下降太多,不利于正确读出,会影响器件的可靠性。(4

S/R电路设计和性能及主要重点技术措施分析设计性能好的S/R要求综合考虑如下四点。(1)高灵敏度S/R灵敏度越高,允许单元的存储电容越小,集成容量越大。(2)低功耗由于VLSI DRAM中S/R众多,因此它们的功耗直接影响DRAM的总功耗。为此采用全动态检测,以避免直流通路引起的可观功耗。(3)高终态“1”电平全动态检测不可避免会有高电平的损失。但下降太多,不利于正确读出,会影响器件的可靠性。(4

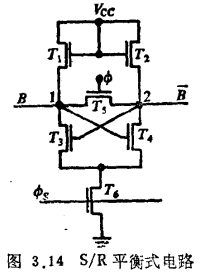

详解灵敏恢复(S/R)放大器的工作原理和分析S/R放大器实际上是一种特殊的电压比较器。如图3.13所示,被比较的输入电压中一个是从选中单元读出,另一个是从虚单元读出,它们既是输入,又是输出。初始电平差经S/R的放大,使的电平差拉开,形成“0”和“1”电平,通过y译码器向外输出。此放大器除了放大功能外,还有恢复、刷新能力,这是DRAM电路所要求的。由于在上预充的电平较高,对存“0”单元是破坏性读出。

详解灵敏恢复(S/R)放大器的工作原理和分析S/R放大器实际上是一种特殊的电压比较器。如图3.13所示,被比较的输入电压中一个是从选中单元读出,另一个是从虚单元读出,它们既是输入,又是输出。初始电平差经S/R的放大,使的电平差拉开,形成“0”和“1”电平,通过y译码器向外输出。此放大器除了放大功能外,还有恢复、刷新能力,这是DRAM电路所要求的。由于在上预充的电平较高,对存“0”单元是破坏性读出。

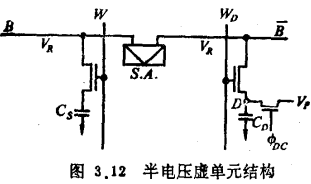

灵敏恢复放大器-虚单元的设置(半电荷/半电压)设计方案详解一、虚单元的设置大容量DRAM位线电容CB大,存储电容Cs小,因而只能得到较小的读出讯号。这个小讯号需要正确放大,放大器要有高的灵敏度和抗干扰能力。如图3.10所示,如果一条位线上有64个单元,可将它们均衡地安排在放大器的两边。如将位线电位预充到VS0(单元存“0”电平)和VS1(单元存“1”电平)之间某一参考电平,则当通过字线打开门管时,

灵敏恢复放大器-虚单元的设置(半电荷/半电压)设计方案详解一、虚单元的设置大容量DRAM位线电容CB大,存储电容Cs小,因而只能得到较小的读出讯号。这个小讯号需要正确放大,放大器要有高的灵敏度和抗干扰能力。如图3.10所示,如果一条位线上有64个单元,可将它们均衡地安排在放大器的两边。如将位线电位预充到VS0(单元存“0”电平)和VS1(单元存“1”电平)之间某一参考电平,则当通过字线打开门管时,

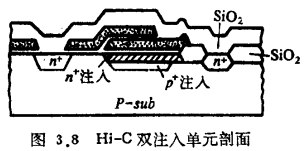

MOS管 VLSI随机存储器设计方案及其剖面图解析随机存储器(RAM)是VLSI的代表产品,是用量最多的VLSI品种。随着工艺水平的飞速进步,RAM的集成度提高很快,在70年代初期单片容量为1K位,80年代中期已达到4M位。RAM是规则结构,每个存储单元都是完全重复一致的,便于设计。因此,在开发VLSI工艺时一般用它作为先导产品。由于软件技术和人工智能发展的需要,对价廉、大容量的RAM的要求更为迫

MOS管 VLSI随机存储器设计方案及其剖面图解析随机存储器(RAM)是VLSI的代表产品,是用量最多的VLSI品种。随着工艺水平的飞速进步,RAM的集成度提高很快,在70年代初期单片容量为1K位,80年代中期已达到4M位。RAM是规则结构,每个存储单元都是完全重复一致的,便于设计。因此,在开发VLSI工艺时一般用它作为先导产品。由于软件技术和人工智能发展的需要,对价廉、大容量的RAM的要求更为迫