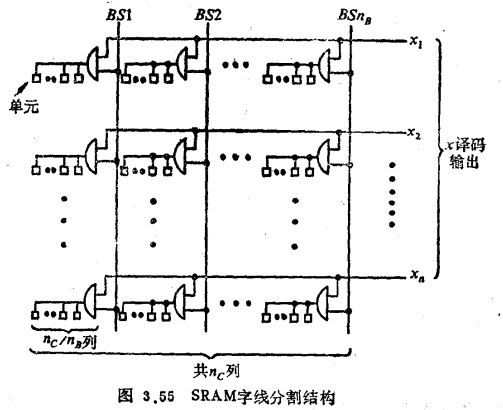

VLSI SRAM字线分割技术(DWL)的电流电路及结构分析SRAM规模的增大,引起列线的电流增加,而限制了维持功耗的降低。SRAM不同于DRAM,在维持状态下总有一条字线是高电平,列电流通过位线负载管、单元门管和工作管流到Vss。图3.54为列电流的通路。列数越多,列电流越大。列电流与单元负载的形式无关,也就是说总的列电流主要决定于一条字线所驱动的单元数,字线越长,问题越严重。此外,随着SRAM

VLSI SRAM字线分割技术(DWL)的电流电路及结构分析SRAM规模的增大,引起列线的电流增加,而限制了维持功耗的降低。SRAM不同于DRAM,在维持状态下总有一条字线是高电平,列电流通过位线负载管、单元门管和工作管流到Vss。图3.54为列电流的通路。列数越多,列电流越大。列电流与单元负载的形式无关,也就是说总的列电流主要决定于一条字线所驱动的单元数,字线越长,问题越严重。此外,随着SRAM

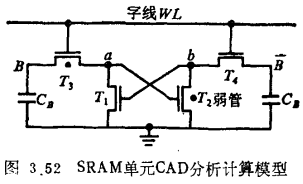

VLSI SRAM单元电路基本原理及其特征解析静态随机存储器(SRAM)集成容量不及DRAM,一般为DRAM的1/4左右,这是因为它的单元电路较为复杂,占硅片面积大。但是它有两个优于DRAM的特点,即不需要刷新,使用方便和速度快。因此,在某些场合,例如高速缓冲存储器(Cache),必须使用SRAM。一、VLSI SRAM单元电路SRAM单元是由六个器件组成的触发器,触发器彼此的不同主要在于负载器件

VLSI SRAM单元电路基本原理及其特征解析静态随机存储器(SRAM)集成容量不及DRAM,一般为DRAM的1/4左右,这是因为它的单元电路较为复杂,占硅片面积大。但是它有两个优于DRAM的特点,即不需要刷新,使用方便和速度快。因此,在某些场合,例如高速缓冲存储器(Cache),必须使用SRAM。一、VLSI SRAM单元电路SRAM单元是由六个器件组成的触发器,触发器彼此的不同主要在于负载器件

Mb级DRAM的位线半电压预充措施方法技术分析以往采用位线预充到Vcc高电平的方法有不少缺点。改用Vcc/2预充有如下改进之处:1、由于位线电平摆幅减小一倍,可加快电路速度,同时使位线与衬底之间的耦合噪音也缩减一倍。2、减少对位线的预充电流,降低功耗。3、门管的漏电压降低,大大减弱短沟管的DIBL效应,以利数据保存。4、降低对单元电荷传输所要求的字线电平,只要求达到(Vcc/2)+VT,使S/R可

Mb级DRAM的位线半电压预充措施方法技术分析以往采用位线预充到Vcc高电平的方法有不少缺点。改用Vcc/2预充有如下改进之处:1、由于位线电平摆幅减小一倍,可加快电路速度,同时使位线与衬底之间的耦合噪音也缩减一倍。2、减少对位线的预充电流,降低功耗。3、门管的漏电压降低,大大减弱短沟管的DIBL效应,以利数据保存。4、降低对单元电荷传输所要求的字线电平,只要求达到(Vcc/2)+VT,使S/R可

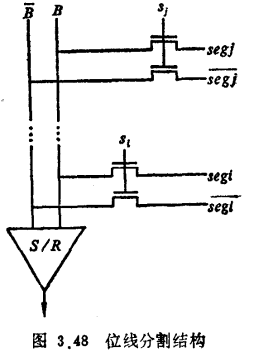

Mb级DRAM分割位线结构基本电路分析Mb级DRAM的位线和字线很长,引起很多问题。例如,位线长,分布参量大,特别是Ca大会使读出讯号小,速度慢。位线分割成几个子段可以解决上述问题。如果用通常的方法要增加不少译码器和灵敏放大器,会使芯片面积增加不少。新的位线分割结构如图3.48所示,采用分段选择、共享S/R的设计,可以大大节省芯片面积。

Mb级DRAM分割位线结构基本电路分析Mb级DRAM的位线和字线很长,引起很多问题。例如,位线长,分布参量大,特别是Ca大会使读出讯号小,速度慢。位线分割成几个子段可以解决上述问题。如果用通常的方法要增加不少译码器和灵敏放大器,会使芯片面积增加不少。新的位线分割结构如图3.48所示,采用分段选择、共享S/R的设计,可以大大节省芯片面积。

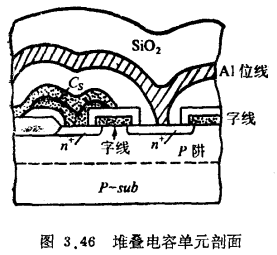

解析Mb级DRAM缩小单元面积和剖面及结构方案随着数字技术的飞速发展,要求内存容量越来越大。大型机为Gb字节容量,大量普及的个人计算机(PC)也要求Mb字节容量。半导体存储器的市场需求正在迅速增长。这些因素促使DRAM技术不断改进,集成度不断提高,Mb级容量的DRAM已开发成功,并投放市场。本节针对Mb级DRAM讨论提高集成容量的主要措施及其限制。缩小单元面积缩小光刻尺寸是缩小单元面积的前提,至今

解析Mb级DRAM缩小单元面积和剖面及结构方案随着数字技术的飞速发展,要求内存容量越来越大。大型机为Gb字节容量,大量普及的个人计算机(PC)也要求Mb字节容量。半导体存储器的市场需求正在迅速增长。这些因素促使DRAM技术不断改进,集成度不断提高,Mb级容量的DRAM已开发成功,并投放市场。本节针对Mb级DRAM讨论提高集成容量的主要措施及其限制。缩小单元面积缩小光刻尺寸是缩小单元面积的前提,至今

CMOS DRAM几种关键电路的设计解析(S/R放大器、行译码器等)几种关键电路的设计1、灵敏/恢复(S/R)放大器用CMOS电路设计S/R SAS可以十分简单。图3.42就是用两对PMOS和NMOS管组成的S/R。当上建立了小电平差后,SAS出现一个正脉冲,向充电,由交叉耦合的P管把它们的电平差放大,结果两个P管一开一关。开的一边达高电平VDD,关的一边为略高于Vss的低电平,后在点出现一个负脉

CMOS DRAM几种关键电路的设计解析(S/R放大器、行译码器等)几种关键电路的设计1、灵敏/恢复(S/R)放大器用CMOS电路设计S/R SAS可以十分简单。图3.42就是用两对PMOS和NMOS管组成的S/R。当上建立了小电平差后,SAS出现一个正脉冲,向充电,由交叉耦合的P管把它们的电平差放大,结果两个P管一开一关。开的一边达高电平VDD,关的一边为略高于Vss的低电平,后在点出现一个负脉

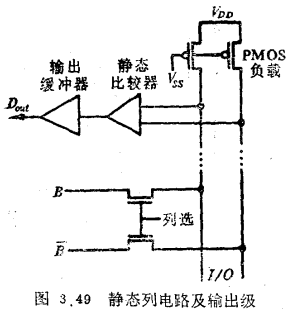

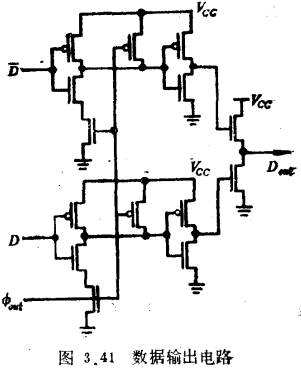

CMOS DRAM外围电路分类及基础电路分析外围电路分为两类:1、没有时序要求的电路采用最简单的全静态电路,例如行地址预译码器,见图3.38。2、有时序要求的电路采用有时钟控制的静态电路。按照控制方式不同,又可分成三类:(1)时钟控制驱动如图3.39所示的列译码器电路,要求在灵敏放大后开始工作,因此用时钟фd进行控制。平时фd为高电平,列译码器不工作。当灵敏放大后,фd为低电平,列译码按静态方式工

CMOS DRAM外围电路分类及基础电路分析外围电路分为两类:1、没有时序要求的电路采用最简单的全静态电路,例如行地址预译码器,见图3.38。2、有时序要求的电路采用有时钟控制的静态电路。按照控制方式不同,又可分成三类:(1)时钟控制驱动如图3.39所示的列译码器电路,要求在灵敏放大后开始工作,因此用时钟фd进行控制。平时фd为高电平,列译码器不工作。当灵敏放大后,фd为低电平,列译码按静态方式工

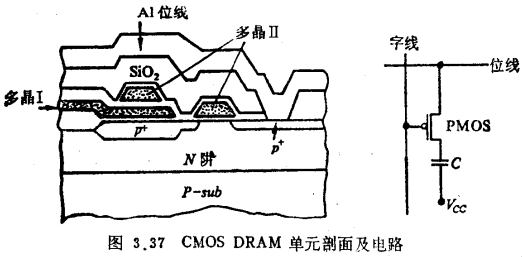

详解CMOS DRAM单元剖面及电路基本组成分析CMOS技术的发展为VLSI DRAM的设计提供了更好的工艺技术和电路形式,与NMOS相比,显示出多方面的优越性。从80年代中期开始,CMOS DRAM已经取代了NMOS DRAM,并已达到Mb级水平。NMOS DRAM采用动态工作方式,利用时钟预充和电容自举达到低功耗及好的输出高电平,因此时钟多,电路复杂,影响工作速度。CMOS电路具有无静态功耗、

详解CMOS DRAM单元剖面及电路基本组成分析CMOS技术的发展为VLSI DRAM的设计提供了更好的工艺技术和电路形式,与NMOS相比,显示出多方面的优越性。从80年代中期开始,CMOS DRAM已经取代了NMOS DRAM,并已达到Mb级水平。NMOS DRAM采用动态工作方式,利用时钟预充和电容自举达到低功耗及好的输出高电平,因此时钟多,电路复杂,影响工作速度。CMOS电路具有无静态功耗、

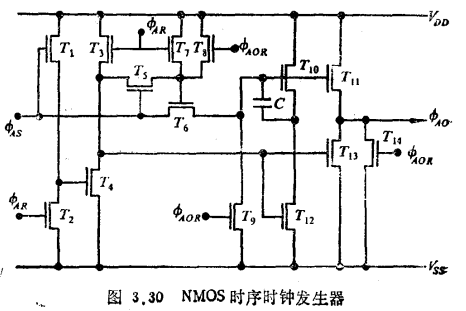

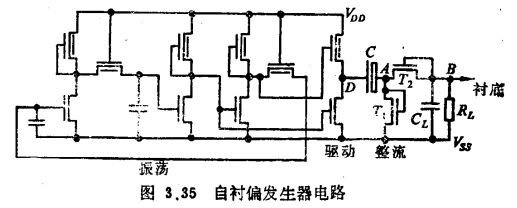

详解NMOS DRAM自衬偏发生器特性及其优势分析目前的DRAM产品都是单+5V电源供电,在芯片内部有一个电压发生器,它的电压为-3V左右,作为加在衬底上的负偏压,以VBB表示。VBB在片内的存在用户从外特性是看不到的,但对改善DRAM的性能有很多的好处:1、防止负过冲引起“1”单元失效如图3.34所示的动态电路,原来结点2为高电平,输出结点1为低电平,T2处于关闭状态。当结点2在t时刻跳变到低电

详解NMOS DRAM自衬偏发生器特性及其优势分析目前的DRAM产品都是单+5V电源供电,在芯片内部有一个电压发生器,它的电压为-3V左右,作为加在衬底上的负偏压,以VBB表示。VBB在片内的存在用户从外特性是看不到的,但对改善DRAM的性能有很多的好处:1、防止负过冲引起“1”单元失效如图3.34所示的动态电路,原来结点2为高电平,输出结点1为低电平,T2处于关闭状态。当结点2在t时刻跳变到低电

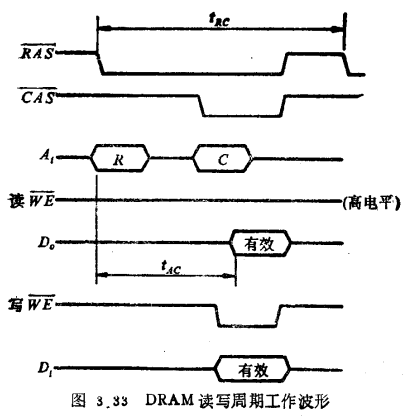

NMOS DRAM性能指标和读写周期工作波形图分析DRAM内部虽然电路比较复杂,有众多的时钟,但是从外特性来看是十分简单的。例如,一个标准256K DRAM,采用16腿的双立直插封装,16腿的分配为电源、地、输出,输入、9个地址(行、列共用)、3个外控制时钟、和。图3.33为DRAM读出写入的工作波形。它是周期性工作,一个周期内包括预充时间和工作时间两部分,这体现在的波形上,高电平为预充,低电平为

NMOS DRAM性能指标和读写周期工作波形图分析DRAM内部虽然电路比较复杂,有众多的时钟,但是从外特性来看是十分简单的。例如,一个标准256K DRAM,采用16腿的双立直插封装,16腿的分配为电源、地、输出,输入、9个地址(行、列共用)、3个外控制时钟、和。图3.33为DRAM读出写入的工作波形。它是周期性工作,一个周期内包括预充时间和工作时间两部分,这体现在的波形上,高电平为预充,低电平为